VY22549A硬件实现控制单元电路

发布时间:2019/10/25 17:36:59 访问次数:834

VY22549A如果rL・s=o,则系统保持在So状态。图中未画出四种状态下主干

民/ST道和支干道交通灯的输出情况,它们是四种状态的组合输出。sT是控制单元的输出信号。

时钟脉冲产生器由石英晶体组成(见第8章)。下面主要介绍用中规模集成电

路设计交通灯控制系统。交通灯控制单元状态图,设计控制单元电路.

用硬件实现控制单元电路的方法有很多,这里主要介绍触发器状态组合和一个触发器对应一个状态的方法。下面用触发器状态组合方法设计交通灯控制单元。

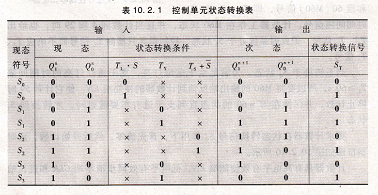

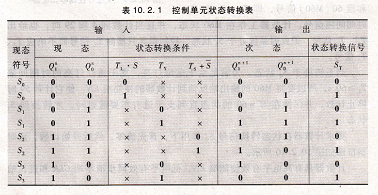

根据图10.2,8所示状态图可知,交通灯控制单元有4种状态,选用两个触发器FF1、FFO的4种输出组合对其进行编码,可以列出状态转换表,如表10.2.1所示,控制单元状态转换的条件为rL・s、rv和rs+s。Reser信号将控制单元置为初始状态OlQ:=00以后,如果rL・s=0,则控制单元保持在00状态;如果rL・s=1,则控制器转换到OI+10:+1=01状态。这两种情况与条件TY和rs+S无关,所以用无关项“×”表示。其余情况依此类推,同时表中列出状态转换信号ST。

前面介绍的中、小规模组合逻辑集成器件性能好、结构简单,因而成为组成数字系统的基本构件。但是对于一个大型复杂的数字系统,过多的器件可能导致功耗高、占用空间大和系统可靠性差等问题。利用可编程逻辑器件进行数字系统的设计,可以较好地解决以上问题。可编程逻辑器件是一种可以由用户定义和设置逻辑功能的器件。该类器件具有逻辑功能实现灵活、集成度高、处

理速度快和可靠性高等特点。

PLD的一般结构框图如图4,5.1(a)所示。与阵列和或阵列输入是它的基本组成

部分,通过对与、或阵列的编程实现所需的逻辑功能。输人电路是由输入缓冲

器组成,通过它可以得到驱动能力强,并且互补的输人信号变量送到与阵列。

有些PLD器件的输人电路包含锁存器或寄存器等时序电路。输出电路主要分

为组合和时序两种方式,组合方式的或阵列经过三态门输出,时序方式的或阵

列经过寄存器和三态门输出。有些电路可以根据需要将输出反馈到与阵列的输人,以增加器件的灵活性。图4.5,1(b)所示为PLD基本电路结构,为简明起见,将输出三态门省略。

PLD的表示方法,为了便于绘制与、或阵列的结构图,采用一种简化的表示方法,该方法的各种符号及含义如下。

连接方法,在图4.5.1(b)所示基本的PLD结构中,门阵列的每个交叉点称为“单元”单元的连接方式共有三种情况,如图4.5,2所示:

硬线连接。硬线连接是固定连接,不可以编程改变。 PLD连接符号

可编程“接通”单元。它依靠用户编程来实现“接通”连接。

可编程“断开”单元。编程实现断开状态。这种单元又称为被编程擦除单元。

基本门电路的表示方法PLD中基本门电路符号如图4.5.3所示。图4.5.3(a)和图4.5,3(b)分别为与门L1=ABC和或门无2=处+B+C。由于L3=AAB B=0,图4.5.3(c)给出了与门输出恒等于0的简化画法。图4.5,3(d)中与门的所有输入项均不接通,保持“悬浮”的1状态,即L4=1。图4.5.3(e)为具有互补输出的输入缓冲器。图4.5.3(f)为三态输出缓冲器。

编程连接技术,早期的PLD采用双极型连接技术,对于图4.5.4(a)的逻辑电路,单元的连接是由一个二极管与金属熔丝串接在一起,如图4,5.4(b)所示。编程时,用比工作电流大许多的电流,将不需要连接的熔丝烧断。由于熔丝烧断后不能恢复,这种方法只能进行一次编程。在门阵列中表示“单元”连接状况的阵

列图,称为熔丝图,并且这个名称被沿用下来。

在CMOs的PLD中,常采用可擦除的编程方法,即可以对器件进行多次编程。可擦除CMOs技术用浮栅MOs管代替“熔丝”,如图4.5.4(c)所示,图中MOs管为浮栅MOs符号,它可以是叠栅注人MOs、浮栅隧道氧化层MOs.

VY22549A如果rL・s=o,则系统保持在So状态。图中未画出四种状态下主干

民/ST道和支干道交通灯的输出情况,它们是四种状态的组合输出。sT是控制单元的输出信号。

时钟脉冲产生器由石英晶体组成(见第8章)。下面主要介绍用中规模集成电

路设计交通灯控制系统。交通灯控制单元状态图,设计控制单元电路.

用硬件实现控制单元电路的方法有很多,这里主要介绍触发器状态组合和一个触发器对应一个状态的方法。下面用触发器状态组合方法设计交通灯控制单元。

根据图10.2,8所示状态图可知,交通灯控制单元有4种状态,选用两个触发器FF1、FFO的4种输出组合对其进行编码,可以列出状态转换表,如表10.2.1所示,控制单元状态转换的条件为rL・s、rv和rs+s。Reser信号将控制单元置为初始状态OlQ:=00以后,如果rL・s=0,则控制单元保持在00状态;如果rL・s=1,则控制器转换到OI+10:+1=01状态。这两种情况与条件TY和rs+S无关,所以用无关项“×”表示。其余情况依此类推,同时表中列出状态转换信号ST。

前面介绍的中、小规模组合逻辑集成器件性能好、结构简单,因而成为组成数字系统的基本构件。但是对于一个大型复杂的数字系统,过多的器件可能导致功耗高、占用空间大和系统可靠性差等问题。利用可编程逻辑器件进行数字系统的设计,可以较好地解决以上问题。可编程逻辑器件是一种可以由用户定义和设置逻辑功能的器件。该类器件具有逻辑功能实现灵活、集成度高、处

理速度快和可靠性高等特点。

PLD的一般结构框图如图4,5.1(a)所示。与阵列和或阵列输入是它的基本组成

部分,通过对与、或阵列的编程实现所需的逻辑功能。输人电路是由输入缓冲

器组成,通过它可以得到驱动能力强,并且互补的输人信号变量送到与阵列。

有些PLD器件的输人电路包含锁存器或寄存器等时序电路。输出电路主要分

为组合和时序两种方式,组合方式的或阵列经过三态门输出,时序方式的或阵

列经过寄存器和三态门输出。有些电路可以根据需要将输出反馈到与阵列的输人,以增加器件的灵活性。图4.5,1(b)所示为PLD基本电路结构,为简明起见,将输出三态门省略。

PLD的表示方法,为了便于绘制与、或阵列的结构图,采用一种简化的表示方法,该方法的各种符号及含义如下。

连接方法,在图4.5.1(b)所示基本的PLD结构中,门阵列的每个交叉点称为“单元”单元的连接方式共有三种情况,如图4.5,2所示:

硬线连接。硬线连接是固定连接,不可以编程改变。 PLD连接符号

可编程“接通”单元。它依靠用户编程来实现“接通”连接。

可编程“断开”单元。编程实现断开状态。这种单元又称为被编程擦除单元。

基本门电路的表示方法PLD中基本门电路符号如图4.5.3所示。图4.5.3(a)和图4.5,3(b)分别为与门L1=ABC和或门无2=处+B+C。由于L3=AAB B=0,图4.5.3(c)给出了与门输出恒等于0的简化画法。图4.5,3(d)中与门的所有输入项均不接通,保持“悬浮”的1状态,即L4=1。图4.5.3(e)为具有互补输出的输入缓冲器。图4.5.3(f)为三态输出缓冲器。

编程连接技术,早期的PLD采用双极型连接技术,对于图4.5.4(a)的逻辑电路,单元的连接是由一个二极管与金属熔丝串接在一起,如图4,5.4(b)所示。编程时,用比工作电流大许多的电流,将不需要连接的熔丝烧断。由于熔丝烧断后不能恢复,这种方法只能进行一次编程。在门阵列中表示“单元”连接状况的阵

列图,称为熔丝图,并且这个名称被沿用下来。

在CMOs的PLD中,常采用可擦除的编程方法,即可以对器件进行多次编程。可擦除CMOs技术用浮栅MOs管代替“熔丝”,如图4.5.4(c)所示,图中MOs管为浮栅MOs符号,它可以是叠栅注人MOs、浮栅隧道氧化层MOs.

上一篇:XC61AN1102PR摩根定理

公网安备44030402000607

公网安备44030402000607