LTC3731CGPBF 进位及控制逻辑

发布时间:2019/10/21 17:47:12 访问次数:691

LTC3731CGPBF部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

可编程逻辑模块CLB

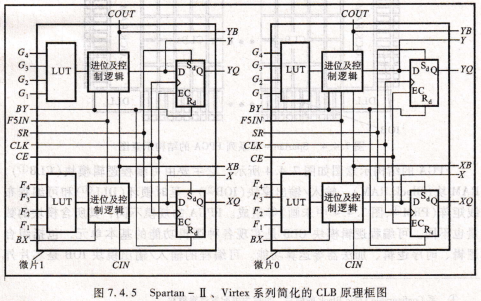

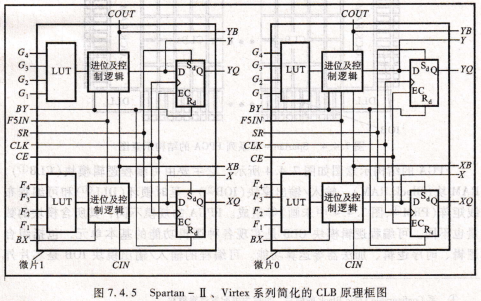

CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。

三个双联开关控制两盏灯示意图,继电器应用电路,三极管驱动继电器 当三极管用来驱动继电器工作时,笔者推荐采用NPN型的三极管。电路工作原理如图11-17所示。当输人高电平时,三极管Q1饱和导通,继电器线圈通电,触点吸合。当输入低电平时,三极管Q1截止,继电器线圈断电,触点断开。三极管放大倍数`一般选择在120~240之间,驱动继电器的二极管必须选插件封装。

一般R1阻值选取,保证基极电流的大小在1.5mA左右。具体选值的大小要根据继电器实际情况而定。一般情况下R1阻值的大小为2kΩ。当单片机(MCU)与三极管之间的距离在15cm以Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图.

实际上,PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。Logic Cell的缩写。

LTC3731CGPBF部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

可编程逻辑模块CLB

CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。

三个双联开关控制两盏灯示意图,继电器应用电路,三极管驱动继电器 当三极管用来驱动继电器工作时,笔者推荐采用NPN型的三极管。电路工作原理如图11-17所示。当输人高电平时,三极管Q1饱和导通,继电器线圈通电,触点吸合。当输入低电平时,三极管Q1截止,继电器线圈断电,触点断开。三极管放大倍数`一般选择在120~240之间,驱动继电器的二极管必须选插件封装。

一般R1阻值选取,保证基极电流的大小在1.5mA左右。具体选值的大小要根据继电器实际情况而定。一般情况下R1阻值的大小为2kΩ。当单片机(MCU)与三极管之间的距离在15cm以Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图.

实际上,PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。Logic Cell的缩写。

公网安备44030402000607

公网安备44030402000607