QL2007 5个连续编码

发布时间:2019/10/17 21:25:53 访问次数:1042

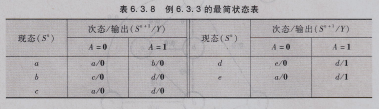

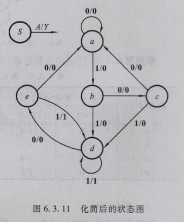

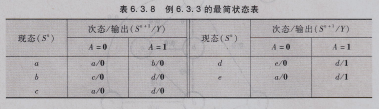

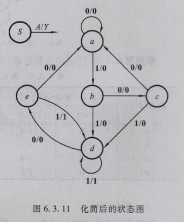

QL2007再观察表6.3.7,又出现状态d和F是等价的,状态F亦可去除,代之以d。于是,得到表6,3,8所示的状态表。检查该表,已不存在等价状态,因此是最简状态表。根据表6.3.8画出的状态图如图6,3.11所示。

表6,3.8 例6.3.3的最简状态表

上述状态化简过程将原有的7个状态化简为5个,而输人一输出特性与原始状态表和原始状态图完全相同。

状态分配

表6.3.8中列出5个状态,最简单的状态分配是使用自然二进制码,取进制计数序列的前5个连续编码,如6.3,9中的状态分配方案1。结合6.3.11可以看出,这种二进制编码值递增顺序基本上与相应的状态转换顺一致。对于较简单的时序电路,按这状态分配方案构成的时序电路,其组合电路将可能相对简单一些。

表6,3.9中所列方案2为格雷码方案。如果状态图所示的主要状态转换顺序是简单的从o到e,那么它从一个状态转换到下一状再观察表6.3.7,又出现状态d和F是等价的,状态F亦可去除,代之以d。于是,得到表6,3,8所示的状态表。检查该表,已不存在等价状态,因此是最简状态表。根据表6.3.8画出的状态图如图6,3.11所示。

表6,3.8 例6.3.3的最简状态表

上述状态化简过程将原有的7个状态化简为5个,而输人一输出特性与原始状态表和原始状态图完全相同。

(3)状态分配表6.3.8中列出5个状态,最简单的状态分配是使用自然二进制码,取

进制计数序列的前5个连续编码,如6.3,9中的状态分配方案1。结合6.3.11可以看出,这种二进制编码值递增顺序基本上与相应的状态转换顺一致。对于较简单的时序电路,按这状态分配方案构成的时序电路,其组电路将可能相对简单一些。

表6,3.9中所列方案2为格雷码方案。如果状态图所示的主要状态转换顺序是简单的从o到e,那么它从一个状3.11 化简后的状态图电路的可靠性。

虽然这将使用较多的触,有些国外文献称之为“0ne~Hot Encoding”,国内某些文献直译为“1位热码编码”。态转换到下状态,使用表6.3.发器,但它的编码方式非常简单,可有效地简化组合电路,并且还可以提高工作可靠性和工作速度。在大规模可编程逻辑器件,例如FPGA(见7.4节)中,触发器数量较多而门逻辑相对较少,“一对一”的编码方案有时反而更有利于提高器件资源的利用率。

化简后的状态图电路的可靠性。

9中所虽然这将使用较多的触

有些国外文献称之为“0ne~Hot Encoding”,国内某些文献直译为“1位热码编码”。态转换到下状态,使用表6.3.发器,但它的编码方式非常简单,可有效地简化组合电路,并且还可以提高工作可靠性和工作速度。在大规模可编程逻辑器件,例如FPGA(见7.4节)中,触发器数量较多而门逻辑相对较少,“一对一”的编码方案有时反而更有利于提高器件资源的利用率。

QL2007再观察表6.3.7,又出现状态d和F是等价的,状态F亦可去除,代之以d。于是,得到表6,3,8所示的状态表。检查该表,已不存在等价状态,因此是最简状态表。根据表6.3.8画出的状态图如图6,3.11所示。

表6,3.8 例6.3.3的最简状态表

上述状态化简过程将原有的7个状态化简为5个,而输人一输出特性与原始状态表和原始状态图完全相同。

状态分配

表6.3.8中列出5个状态,最简单的状态分配是使用自然二进制码,取进制计数序列的前5个连续编码,如6.3,9中的状态分配方案1。结合6.3.11可以看出,这种二进制编码值递增顺序基本上与相应的状态转换顺一致。对于较简单的时序电路,按这状态分配方案构成的时序电路,其组合电路将可能相对简单一些。

表6,3.9中所列方案2为格雷码方案。如果状态图所示的主要状态转换顺序是简单的从o到e,那么它从一个状态转换到下一状再观察表6.3.7,又出现状态d和F是等价的,状态F亦可去除,代之以d。于是,得到表6,3,8所示的状态表。检查该表,已不存在等价状态,因此是最简状态表。根据表6.3.8画出的状态图如图6,3.11所示。

表6,3.8 例6.3.3的最简状态表

上述状态化简过程将原有的7个状态化简为5个,而输人一输出特性与原始状态表和原始状态图完全相同。

(3)状态分配表6.3.8中列出5个状态,最简单的状态分配是使用自然二进制码,取

进制计数序列的前5个连续编码,如6.3,9中的状态分配方案1。结合6.3.11可以看出,这种二进制编码值递增顺序基本上与相应的状态转换顺一致。对于较简单的时序电路,按这状态分配方案构成的时序电路,其组电路将可能相对简单一些。

表6,3.9中所列方案2为格雷码方案。如果状态图所示的主要状态转换顺序是简单的从o到e,那么它从一个状3.11 化简后的状态图电路的可靠性。

虽然这将使用较多的触,有些国外文献称之为“0ne~Hot Encoding”,国内某些文献直译为“1位热码编码”。态转换到下状态,使用表6.3.发器,但它的编码方式非常简单,可有效地简化组合电路,并且还可以提高工作可靠性和工作速度。在大规模可编程逻辑器件,例如FPGA(见7.4节)中,触发器数量较多而门逻辑相对较少,“一对一”的编码方案有时反而更有利于提高器件资源的利用率。

化简后的状态图电路的可靠性。

9中所虽然这将使用较多的触

有些国外文献称之为“0ne~Hot Encoding”,国内某些文献直译为“1位热码编码”。态转换到下状态,使用表6.3.发器,但它的编码方式非常简单,可有效地简化组合电路,并且还可以提高工作可靠性和工作速度。在大规模可编程逻辑器件,例如FPGA(见7.4节)中,触发器数量较多而门逻辑相对较少,“一对一”的编码方案有时反而更有利于提高器件资源的利用率。

公网安备44030402000607

公网安备44030402000607