电容值大小对电源去耦效果的影响

发布时间:2019/1/10 21:36:12 访问次数:516

电容值大小对电源去耦效果的影响 LFE2-12E-5F484C

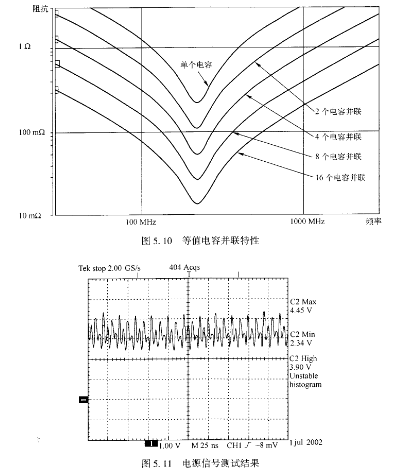

时钟驱动芯片××38OT,很多数字电路硬件开发工程师都很熟悉,就是这个东西(本案例中是3.3Ⅴ供电),在某一设备的电路上工作时,发现其电源引脚上用示波器测试到的波形如图5.11所示。

从图5.11中可以看出,波形的峰-峰值为1.8Ⅴ,频率接近100MHz,显然不符合电源质量的要求(通常要求为5%)。电源噪声直接影响着电源平面和地平面的完整性,对所在系统的共模辐射也有很大影响。PCB上信号的共模辐射模型如图5.12所示。

从高频角度考虑,参考平面(包括地平面和电源平于回流导体,可能有任何频率大小的压降。这个于差模电流JDM在印制线下面的参考平面上会产模电压降叱M,如图5.12所示。这个电压激励大构,产生共模电流几M。例如,通过低阻抗连接面的电缆屏蔽层上的共模电流。

电容值大小对电源去耦效果的影响 LFE2-12E-5F484C

时钟驱动芯片××38OT,很多数字电路硬件开发工程师都很熟悉,就是这个东西(本案例中是3.3Ⅴ供电),在某一设备的电路上工作时,发现其电源引脚上用示波器测试到的波形如图5.11所示。

从图5.11中可以看出,波形的峰-峰值为1.8Ⅴ,频率接近100MHz,显然不符合电源质量的要求(通常要求为5%)。电源噪声直接影响着电源平面和地平面的完整性,对所在系统的共模辐射也有很大影响。PCB上信号的共模辐射模型如图5.12所示。

从高频角度考虑,参考平面(包括地平面和电源平于回流导体,可能有任何频率大小的压降。这个于差模电流JDM在印制线下面的参考平面上会产模电压降叱M,如图5.12所示。这个电压激励大构,产生共模电流几M。例如,通过低阻抗连接面的电缆屏蔽层上的共模电流。

上一篇:时钟及驱动部分的原理

公网安备44030402000607

公网安备44030402000607