有效的容性去耦是通过在PCB上适当放置电容来实现的

发布时间:2019/1/10 21:34:00 访问次数:478

为了达到最佳设计效果,需要将354个⒛nF的电容平均分布在整个PCB上。 L9785MD0但是从实际情况来看,这么多电容往往是不太可能的,如果同时开关的数目减少,上升沿不是很快,允许电压波动的范围更大,计算出来的结果也会变化很大。如果实际的高速电路要求很高,只有尽可能选取E比较小的电容来避免使用大量的电容。

有效的容性去耦是通过在PCB上适当放置电容来实现的。随意放置或过度使用电容是对材料的浪费。有时战略性地放几个电容将起到很好的去耦效果。在实际的应用中,两个电容并联使用能提供更宽的抑制带宽。这两个并联电容必须有不同的数量级(如0.1uF和

0.001uF)或容值相差100倍,以达到最佳的效果。

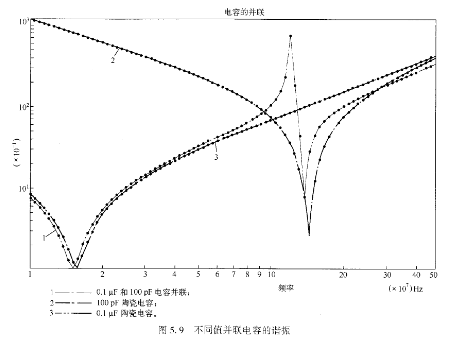

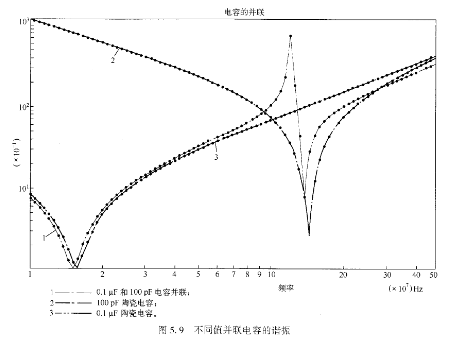

图5.9显示了0.1uF和100pF两个去耦电容单独使用和并联使用时的曲线。0.1uF电容的自谐振频率为14.85MHz,1OO pF电容的自谐振频率是148.5MHz。在110MHz上,因为并联电容的结合阻抗有一个很大的上升,0.1uF电容变成了感性的,而100pF的电容仍为容性的。在这个频率范围内存在一个并联谐振LC电路。在谐振时既有电感也有电容,因此,会有一个反共振频率点,在这些谐振点周围,并联电容表现的阻抗要大于它们单个使用时的阻抗,如果在这个点附近一定要满足EMI要求,这将是个风险。 图59 不同值并联电容的谐振可见,为了去除带宽较宽的噪声,常用的方法是在靠近电源引脚的地方放置两个并联电容(如0.1uF和0,CXl1uF)。如果在PCB布局中使用并联电容去耦,一定要保证电容值相差两个数量级或1∞倍。并联电容的总容值不是主要的,重要的因素是由并联电容产生的并联阻抗。为了优化并联去耦的效果和允许使用单个电容,需要减小电容内的引线电感。在电容装到PCB上时会有一定值的布线电感存在。这个线长包括连接电容到平面的过孔的长度。单个或并联去耦电容的引线越短,去耦效果就越好。

另外,两个同值的电容并联,也可以提高去耦的效果和频率,这是因为电容并联后寄生电阻(ESR)和寄生电感(ESL)因并联而减小,对于多个(乃个)同样值的电容来说,并联使用之后,等效电容C变为屁C,等效电感L变为L/瓦,等效ⅡR变为R/PI,但谐振频率不变。同时从能量的角度来看,多个电容并联能向被去耦的器件提供更多的能量(见图5。I0)。

为了达到最佳设计效果,需要将354个⒛nF的电容平均分布在整个PCB上。 L9785MD0但是从实际情况来看,这么多电容往往是不太可能的,如果同时开关的数目减少,上升沿不是很快,允许电压波动的范围更大,计算出来的结果也会变化很大。如果实际的高速电路要求很高,只有尽可能选取E比较小的电容来避免使用大量的电容。

有效的容性去耦是通过在PCB上适当放置电容来实现的。随意放置或过度使用电容是对材料的浪费。有时战略性地放几个电容将起到很好的去耦效果。在实际的应用中,两个电容并联使用能提供更宽的抑制带宽。这两个并联电容必须有不同的数量级(如0.1uF和

0.001uF)或容值相差100倍,以达到最佳的效果。

图5.9显示了0.1uF和100pF两个去耦电容单独使用和并联使用时的曲线。0.1uF电容的自谐振频率为14.85MHz,1OO pF电容的自谐振频率是148.5MHz。在110MHz上,因为并联电容的结合阻抗有一个很大的上升,0.1uF电容变成了感性的,而100pF的电容仍为容性的。在这个频率范围内存在一个并联谐振LC电路。在谐振时既有电感也有电容,因此,会有一个反共振频率点,在这些谐振点周围,并联电容表现的阻抗要大于它们单个使用时的阻抗,如果在这个点附近一定要满足EMI要求,这将是个风险。 图59 不同值并联电容的谐振可见,为了去除带宽较宽的噪声,常用的方法是在靠近电源引脚的地方放置两个并联电容(如0.1uF和0,CXl1uF)。如果在PCB布局中使用并联电容去耦,一定要保证电容值相差两个数量级或1∞倍。并联电容的总容值不是主要的,重要的因素是由并联电容产生的并联阻抗。为了优化并联去耦的效果和允许使用单个电容,需要减小电容内的引线电感。在电容装到PCB上时会有一定值的布线电感存在。这个线长包括连接电容到平面的过孔的长度。单个或并联去耦电容的引线越短,去耦效果就越好。

另外,两个同值的电容并联,也可以提高去耦的效果和频率,这是因为电容并联后寄生电阻(ESR)和寄生电感(ESL)因并联而减小,对于多个(乃个)同样值的电容来说,并联使用之后,等效电容C变为屁C,等效电感L变为L/瓦,等效ⅡR变为R/PI,但谐振频率不变。同时从能量的角度来看,多个电容并联能向被去耦的器件提供更多的能量(见图5。I0)。

上一篇:去耦和旁路电容的选择

上一篇:电容值大小对电源去耦效果的影响

公网安备44030402000607

公网安备44030402000607