组合逻辑电路设计

发布时间:2015/8/18 21:21:39 访问次数:809

一、实验目的

1.掌握组合逻辑电路FDPF5N60NZ的分析与设计方法。

2.学会电路故障的检查与排除。

二、实验原理

组合逻辑电路,是指该电路在任一时刻的输出状态仅由该时刻的输入信号决定,与电路在此信号输入之前的状态无关。组合电路通常由一些逻辑门构成,而许多具有典型功能的组合电路已集成为商品电路。

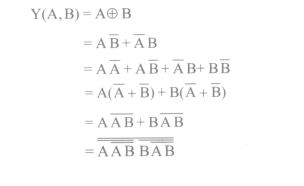

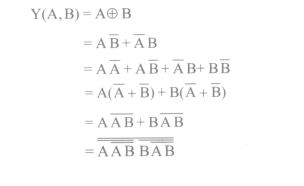

1.用与非门实现异或门逻辑功能

两个变量的异或逻辑函数式为

一、实验目的

1.掌握组合逻辑电路FDPF5N60NZ的分析与设计方法。

2.学会电路故障的检查与排除。

二、实验原理

组合逻辑电路,是指该电路在任一时刻的输出状态仅由该时刻的输入信号决定,与电路在此信号输入之前的状态无关。组合电路通常由一些逻辑门构成,而许多具有典型功能的组合电路已集成为商品电路。

1.用与非门实现异或门逻辑功能

两个变量的异或逻辑函数式为

上一篇:CMOS或门逻辑功能测试

上一篇:与非门实现异或门电路

公网安备44030402000607

公网安备44030402000607