CMOS或门逻辑功能测试

发布时间:2015/8/18 21:20:11 访问次数:968

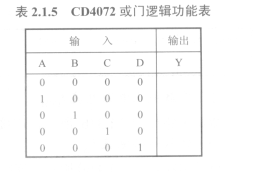

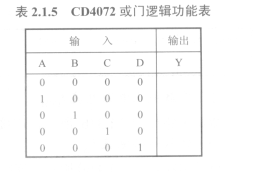

在数字电路实验箱上验证CMOS或门逻辑关系,FDPF18N50将测试结果填入表2.1.5中。

实验主要仪器

1. 74LS20与非门 1片

2.CD4072或门 1片

3.数字电路实验箱 1台

4.万用表及工具 1套

实验报告内容

1.说明门电路的外特性参数测试原理。

2.记录和整理实验测试值,并对结果进行分析。

3.总结实验过程中遇到的问题及其解决方法。

表2.1.5 CD4072或门逻辑功能表

思考题

1.若用TTL与非门74LS20实现Y=AB,则多余输入端如何处理?

2.若用CMOS或门CD4072实现Y=A+B,则多余输入端如何处理?

3.在TTL门电路的外特性参数测试过程中,为什么输入端悬空相当于输入高电平?

在数字电路实验箱上验证CMOS或门逻辑关系,FDPF18N50将测试结果填入表2.1.5中。

实验主要仪器

1. 74LS20与非门 1片

2.CD4072或门 1片

3.数字电路实验箱 1台

4.万用表及工具 1套

实验报告内容

1.说明门电路的外特性参数测试原理。

2.记录和整理实验测试值,并对结果进行分析。

3.总结实验过程中遇到的问题及其解决方法。

表2.1.5 CD4072或门逻辑功能表

思考题

1.若用TTL与非门74LS20实现Y=AB,则多余输入端如何处理?

2.若用CMOS或门CD4072实现Y=A+B,则多余输入端如何处理?

3.在TTL门电路的外特性参数测试过程中,为什么输入端悬空相当于输入高电平?

上一篇:空载截止电源电流/CCH

上一篇:组合逻辑电路设计

公网安备44030402000607

公网安备44030402000607