I2C多路器电路

发布时间:2013/9/6 19:49:55 访问次数:1237

1.用 途

多路器电路。

2.原 理

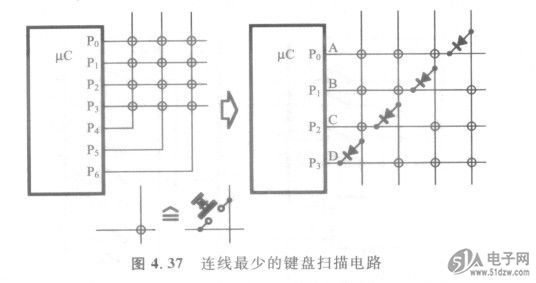

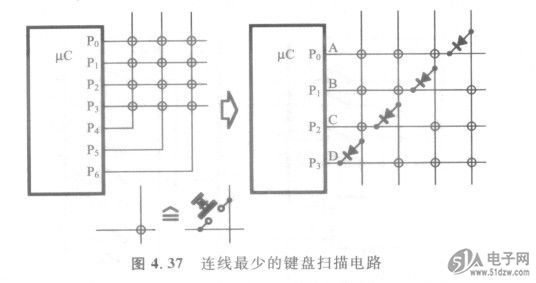

电路如图4.37所示。建立大型I2C数据总线结构时,74HCT374D个别的IC会出现4个或8个地址线不够用,或者SDA和SCL线上的负载容性太大,因而不得不降低总线时钟频率等问题。这个I2C多路器把大型12C数据总线系统分割成几个区域,由I2C总线控制使某些IC与I2C数据总线连接。

12C数据总线设备的工作电压可以为3V,也可以为5V。这里的多路器即使工作电压为3V,它的输入输出都接5V的信号。

图4.37(a)中的PCA9542和PCA9544分别是1到2和1到4多路器,工作电压为2.5~3. 6V(通常为3V)。多路器接通电源时,附属12 C总线被隔离,多路器呈高阻态。为了附属总线之一连接到主I2 C总线,多路器必须首先用自己的I2C地址和一个控制字节访问。为了避免在I2C总线上数据传输的干扰,只有在总线空闲时,才能改变总线连接状态和建立下一个连接。

每个多路器有三个地址接脚(A。、A,、A2),故可以并联使用8个PCA954x。每个I2C区域都有自己的中断线,不同区域的所有的中断线以与( AND)方式连接。中断源区域的I2C总线不是必须连接到主总线上的。所有漏极输出的中断信号“线与”后送到控制器的中断输入。控制器检测到整个系统中的某个地方产生了一个中断信号,则它必须通过查询多路器(通过读出它们的控制字节)的方式确定中断的源区域。在这以后,它可以在可识别的区域中检查相应的设备。只有在产生触发中断的设备已经被访问并且中断已经被响应以后,I2C总线的中断线才被释放。如果在这期间产生了其他的中断,中断线将一直保持为低,控制器将再次查寻触发中断的设备。

图4.38(b)给出了一个I2C总线系统的实例,该系统一部分工作在+3V,另一部分与+5V上拉电阻相连。注意:3V电源电压的上拉电阻比在5V区域中的上拉电阻的阻值大(十倍数)。

1.用 途

多路器电路。

2.原 理

电路如图4.37所示。建立大型I2C数据总线结构时,74HCT374D个别的IC会出现4个或8个地址线不够用,或者SDA和SCL线上的负载容性太大,因而不得不降低总线时钟频率等问题。这个I2C多路器把大型12C数据总线系统分割成几个区域,由I2C总线控制使某些IC与I2C数据总线连接。

12C数据总线设备的工作电压可以为3V,也可以为5V。这里的多路器即使工作电压为3V,它的输入输出都接5V的信号。

图4.37(a)中的PCA9542和PCA9544分别是1到2和1到4多路器,工作电压为2.5~3. 6V(通常为3V)。多路器接通电源时,附属12 C总线被隔离,多路器呈高阻态。为了附属总线之一连接到主I2 C总线,多路器必须首先用自己的I2C地址和一个控制字节访问。为了避免在I2C总线上数据传输的干扰,只有在总线空闲时,才能改变总线连接状态和建立下一个连接。

每个多路器有三个地址接脚(A。、A,、A2),故可以并联使用8个PCA954x。每个I2C区域都有自己的中断线,不同区域的所有的中断线以与( AND)方式连接。中断源区域的I2C总线不是必须连接到主总线上的。所有漏极输出的中断信号“线与”后送到控制器的中断输入。控制器检测到整个系统中的某个地方产生了一个中断信号,则它必须通过查询多路器(通过读出它们的控制字节)的方式确定中断的源区域。在这以后,它可以在可识别的区域中检查相应的设备。只有在产生触发中断的设备已经被访问并且中断已经被响应以后,I2C总线的中断线才被释放。如果在这期间产生了其他的中断,中断线将一直保持为低,控制器将再次查寻触发中断的设备。

图4.38(b)给出了一个I2C总线系统的实例,该系统一部分工作在+3V,另一部分与+5V上拉电阻相连。注意:3V电源电压的上拉电阻比在5V区域中的上拉电阻的阻值大(十倍数)。

上一篇:连线最少的键盘扫描电路

上一篇:串口/并口转换器电路

公网安备44030402000607

公网安备44030402000607