实验电路与说明

发布时间:2012/9/15 12:35:24 访问次数:924

在数字系统中能寄存二Q12P1BXXR24E进制信息,并进行移位的逻辑部件称为移位寄存器。根据移位寄存信息的方式有串人串出、串人并幽、并入串出、并入并出四种形式,按移位方向有左移、右移两种。

本实验采用四位双向通用移位寄存器,型号为74LS194,引脚排列如图6.22所示。DA、DH、Dc、DD为并行输入端;QA、QB、Qc、QD为并行输出端;SR为右移串行输入端;S为左移串行输入端;SI、SO为操作模式控制端;CR为直接无条件清零端;CP为时钟输入端。

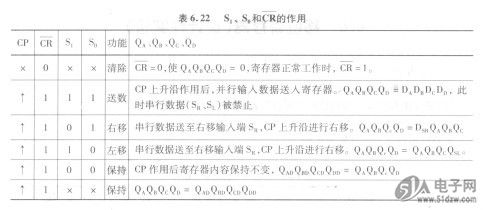

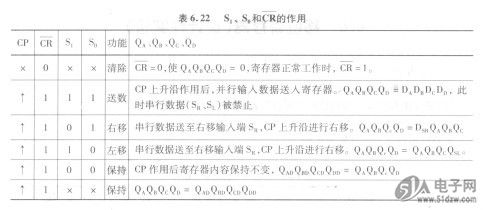

寄存器有四种不同操作模式:①并行寄存;②左移(方向由QA-QI));③右移(方向由QD-QA);④保持。SI、So和CR的作用如表6.22所示。

移位寄存器应用很广,可构成移位寄存器型计数器,顺序脉冲发生器,串行累加器。可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和串行累加器的情况。

把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图6. 23(a)的四位寄存器中,把输出QD和右移串行输入端SR相连接,没初始状态QAQBQCQD=1000,则在时钟脉冲作用下QAQBQCQD将依次变为0100-*0010―0001―1000-+- -…,其波形如图6.23(b)所示。可见它是一个具有四个有效状态的计数器,图6.23(a)电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。

图6.24为累加器原理图。设开始时,被加数和加数已分别存入N+1位累加和移位寄存器和加数移位寄存器中。进位触发器已被清零。

当第一个时钟脉冲到来之前,全加器各输入、输出情况为。在第一个CP脉冲到来后,So存人累加和移位寄存器最高位,存入进位触发器D端,且两个移位寄存器中的内容都向右移动一位,此时全加器输出为S=Al+B1+Co=S1、C=C1。

在第二个CP脉冲到来后,两个移位寄存器的内容又右移一位,此时全加器的输出为S=A7=B2+S2。如此顺序进行,到第N+1个时钟脉冲后,不仅原先存入两个寄存器中的数已被全部移出,且A、B两个数相加的和及最后的进位C1,也被全部存人累加和

在数字系统中能寄存二Q12P1BXXR24E进制信息,并进行移位的逻辑部件称为移位寄存器。根据移位寄存信息的方式有串人串出、串人并幽、并入串出、并入并出四种形式,按移位方向有左移、右移两种。

本实验采用四位双向通用移位寄存器,型号为74LS194,引脚排列如图6.22所示。DA、DH、Dc、DD为并行输入端;QA、QB、Qc、QD为并行输出端;SR为右移串行输入端;S为左移串行输入端;SI、SO为操作模式控制端;CR为直接无条件清零端;CP为时钟输入端。

寄存器有四种不同操作模式:①并行寄存;②左移(方向由QA-QI));③右移(方向由QD-QA);④保持。SI、So和CR的作用如表6.22所示。

移位寄存器应用很广,可构成移位寄存器型计数器,顺序脉冲发生器,串行累加器。可用作数据转换,即把串行数据转换为并行数据,或把并行数据转换为串行数据等。本实验研究移位寄存器用作环形计数器和串行累加器的情况。

把移位寄存器的输出反馈到它的串行输入端,就可以进行循环移位,如图6. 23(a)的四位寄存器中,把输出QD和右移串行输入端SR相连接,没初始状态QAQBQCQD=1000,则在时钟脉冲作用下QAQBQCQD将依次变为0100-*0010―0001―1000-+- -…,其波形如图6.23(b)所示。可见它是一个具有四个有效状态的计数器,图6.23(a)电路可以由各个输出端输出在时间上有先后顺序的脉冲,因此也可作为顺序脉冲发生器。

累加器是由移位寄存器和全加器组成的一种求和电路,它的功能是将本身寄存的数和另一个输入的数相加,并存放在累加器中。

图6.24为累加器原理图。设开始时,被加数和加数已分别存入N+1位累加和移位寄存器和加数移位寄存器中。进位触发器已被清零。

当第一个时钟脉冲到来之前,全加器各输入、输出情况为。在第一个CP脉冲到来后,So存人累加和移位寄存器最高位,存入进位触发器D端,且两个移位寄存器中的内容都向右移动一位,此时全加器输出为S=Al+B1+Co=S1、C=C1。

在第二个CP脉冲到来后,两个移位寄存器的内容又右移一位,此时全加器的输出为S=A7=B2+S2。如此顺序进行,到第N+1个时钟脉冲后,不仅原先存入两个寄存器中的数已被全部移出,且A、B两个数相加的和及最后的进位C1,也被全部存人累加和

上一篇:移位寄存器(设计性实验

上一篇:多谐振荡器与单稳触发器的设计

热门点击

热门点击

- 放大倍数是跨导gM

- RLC串联电路的谐振特性

- 线性有源二端网络等效参数测量

- 方波一三角波发生器设计与研究(设计性实验)

- 乒乓球模拟比赛(综合性实验)

- 关键工序和特殊工序的控制

- 电路图的基本知识

- 连接导线的中断画法规则

- 单稳态触发器

- 观察正弦波信号通过电路时产生的延迟和畸变

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607