以太网接口电路设计

发布时间:2012/4/11 19:47:01 访问次数:2381

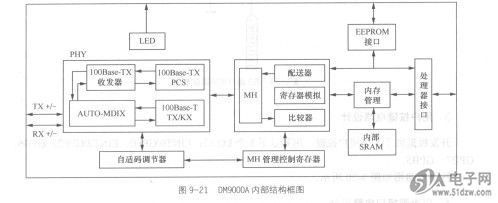

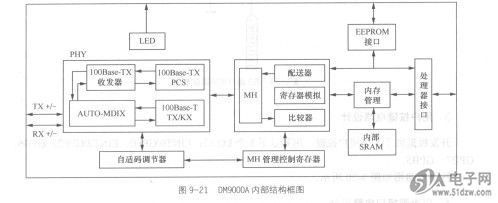

以太网控制器的核心 DSI75-16B选择了DM9000A芯片。DM9000A是中国台湾DAVICOM公司推出的一款高速以太网接口芯片。其基本特征是:集成10/100M物理层接口;内部带有16kB SRAM用于接收发送的FIFO缓存;支持8/16bit两种主机工作模式;通过HP认证的AUTO-Mdix(支持直接互连自动翻转)功能;支持TCP/IP加速(IPv4 check sum offload)诫轻CPU负担,提高整机效能;lOns I/O读写时间。DM9000A以太网控制器遵循IEEE颁布的802.3以太网传输协议。该电路还集成了EEPROM接口,自举时通过EEPROM接口输入到芯片中,从而实现自动初始化。DM9000A内部结构框图和电路原理图如图9-21所示。

系统上电时,ARM920T通过总线配置DM9000A内部网络控制寄存器(NCR)、中断寄存器(ISR)等,完成DM9000A的初始化。随后,DM9000A进入数据收发等待状态。当ARM920T向以太网发送数据时,先将数据打包成UDP或IP数据包,并通过16bit总线发送到DM9000A的数据发送缓存中,然后将数据长度等信息填充到DM9000A的相应寄存器内,使能发送。当DM9000A接收到外部网络送来的以太网数据时,首先检测数据帧的合法性,如果帧头标志有误或存在CRC校验错误,则将该帧数据丢弃,否则将数据帧缓存到内部RAM,并通过中断标志位通知ARM920T,由ARM920T对DM9000A接收到的数据进行处理。

以太网控制器的核心 DSI75-16B选择了DM9000A芯片。DM9000A是中国台湾DAVICOM公司推出的一款高速以太网接口芯片。其基本特征是:集成10/100M物理层接口;内部带有16kB SRAM用于接收发送的FIFO缓存;支持8/16bit两种主机工作模式;通过HP认证的AUTO-Mdix(支持直接互连自动翻转)功能;支持TCP/IP加速(IPv4 check sum offload)诫轻CPU负担,提高整机效能;lOns I/O读写时间。DM9000A以太网控制器遵循IEEE颁布的802.3以太网传输协议。该电路还集成了EEPROM接口,自举时通过EEPROM接口输入到芯片中,从而实现自动初始化。DM9000A内部结构框图和电路原理图如图9-21所示。

系统上电时,ARM920T通过总线配置DM9000A内部网络控制寄存器(NCR)、中断寄存器(ISR)等,完成DM9000A的初始化。随后,DM9000A进入数据收发等待状态。当ARM920T向以太网发送数据时,先将数据打包成UDP或IP数据包,并通过16bit总线发送到DM9000A的数据发送缓存中,然后将数据长度等信息填充到DM9000A的相应寄存器内,使能发送。当DM9000A接收到外部网络送来的以太网数据时,首先检测数据帧的合法性,如果帧头标志有误或存在CRC校验错误,则将该帧数据丢弃,否则将数据帧缓存到内部RAM,并通过中断标志位通知ARM920T,由ARM920T对DM9000A接收到的数据进行处理。

上一篇:USB接口设计

公网安备44030402000607

公网安备44030402000607