AD7265两种封装形式

发布时间:2012/2/26 17:07:03 访问次数:1298

AD7265采用32引脚LFCSP和32引脚TQFP两种封装形式。JK60-065

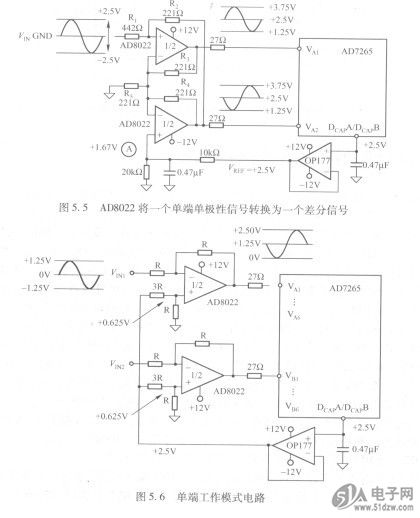

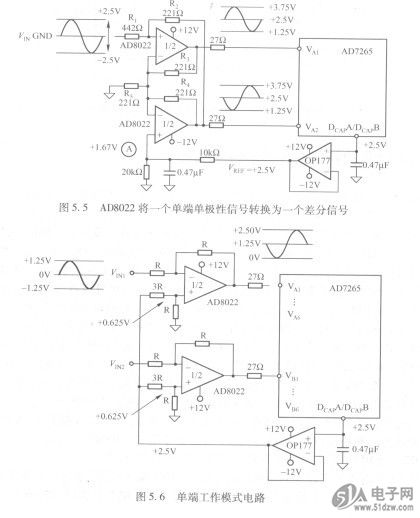

AD7265可以总共有12个单端模拟输入通道。模拟输入范围可通过编程设置为0~VREF,0~2×VREF。在图5.5所示电路中,AD8022将一个单端单号65 3。图5.6所示为用于单端工作模式的电路[65]。在信号源具有高阻抗的应用中,建议先对模拟输入信号进行缓冲,再将信号施加于AD7265的输入端。这可以利用一对双运放,将差分信号直接耦合至AD7265的模拟输入。AD8022是一个双通道、高速、低功耗、低噪声的运算放大器,可用来为AD7265提供一个差分驱动器。在电源电压VD。为5V时,AD7265的最小额定采集时间为90ns,即从该器件进入跟踪模式(第13个SCLK上升沿)到下一次转换(CS下降沿)开始的时间。为AD7265选择的运算放大器必须具有充足的建立时间,以便满足AD7265的采集时间要求,实现额定性能。

在图5.5所示电路中,施加于A点的电压可设置共模电压。图5.5中,A点与基准电压源相连,可以用于设置AD7265额定共模电压范围内的任何值以确定所需的共模电压。如果需要将AD7265的2.5V片内基准电压源用于系统中的其他地方,则如图5.5和图5.6所示,DCAPA和DCAPB的输出必须先经过缓冲。OP177是基准电压源缓冲的理想选择,其精度性能在目前可用的运算放大器中为最高。

AD7265采用32引脚LFCSP和32引脚TQFP两种封装形式。JK60-065

AD7265可以总共有12个单端模拟输入通道。模拟输入范围可通过编程设置为0~VREF,0~2×VREF。在图5.5所示电路中,AD8022将一个单端单号65 3。图5.6所示为用于单端工作模式的电路[65]。在信号源具有高阻抗的应用中,建议先对模拟输入信号进行缓冲,再将信号施加于AD7265的输入端。这可以利用一对双运放,将差分信号直接耦合至AD7265的模拟输入。AD8022是一个双通道、高速、低功耗、低噪声的运算放大器,可用来为AD7265提供一个差分驱动器。在电源电压VD。为5V时,AD7265的最小额定采集时间为90ns,即从该器件进入跟踪模式(第13个SCLK上升沿)到下一次转换(CS下降沿)开始的时间。为AD7265选择的运算放大器必须具有充足的建立时间,以便满足AD7265的采集时间要求,实现额定性能。

在图5.5所示电路中,施加于A点的电压可设置共模电压。图5.5中,A点与基准电压源相连,可以用于设置AD7265额定共模电压范围内的任何值以确定所需的共模电压。如果需要将AD7265的2.5V片内基准电压源用于系统中的其他地方,则如图5.5和图5.6所示,DCAPA和DCAPB的输出必须先经过缓冲。OP177是基准电压源缓冲的理想选择,其精度性能在目前可用的运算放大器中为最高。

热门点击

热门点击

- ADSP-BF561处理器与32位SDRAM

- 电子电路焊接基本知识

- 放大器组成及各元件的作用

- 负反馈放大器的四种基本类型

- 影响器件功耗的主要因素

- 石英晶体――门电路多谐振荡器

- 采用有源负载的共射放大器

- 绝缘栅场效应管

- 光电二极管

- 低功耗看门狗

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607