二极管与门电路工作状况

发布时间:2011/9/6 10:38:55 访问次数:2879

(一)二极管与门电路是怎样工作的? G64128A09BBW00

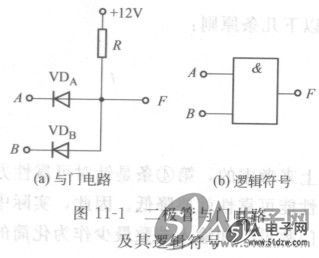

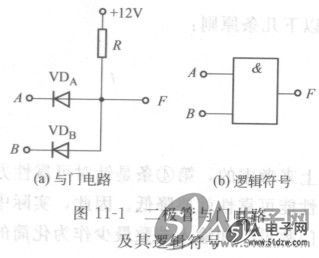

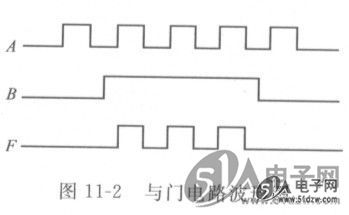

图ll-l(a)是由二极管组成的与门电路,A、B是它的两个输入端,F是输出端。图(b)是它的逻辑符号。

设输入信号电压为3V(高电平1)或OV(低电平O),二极管为理想元件,则电路的工作原理如下。

当输入端A、B都为高电平1时,二极管VDA、VDB均处于正向导通状态,输出端F为高电平(3V)。

当输入端A、B都为低电平O时,二极管VDA、VDB亦处于正向导通状态,输出端F为低电平(OV)。

当输入端一端为高电平、另一端为低电平时,例如A端为3V,B端为OV,则VDB优先导通,输出端F被钳制在OV,输出为低电平。在VDB的钳位作用下,VDA处于截止状态。

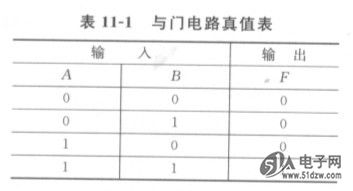

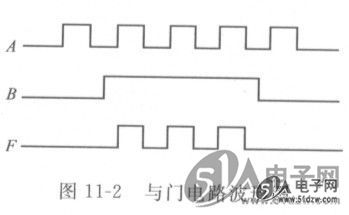

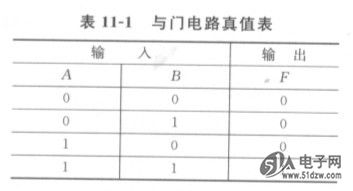

由上述可知,与门电路的输入端中只要有一个为低电平,输出端就是低电平,只有输入端全为高电平时,输出端才是高电平。其真值表如表11―1所示。

由真值表可得出与门电路的逻辑表达式

F=A・B

(二)二极管或门电路是怎样工作的? R3111H601A-T1

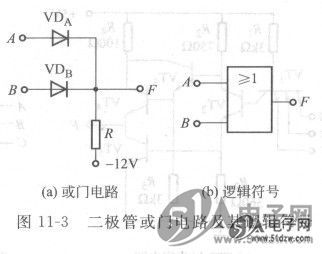

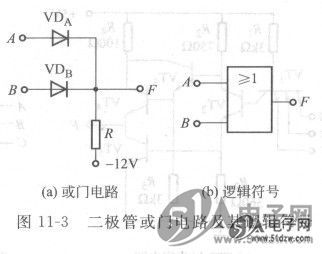

图ll-3(a)是由二极管组成的或门电路,A、B为输入端,F是输出端。图(b)是或门的逻辑符号。工作原理分析如下。

当输入端A、B都处于高电平1(3V)时,则VDA、VDB都处于正向导通状态,输出端F为高电平1(3V)。

当输入端A、B都处于低电平O(OV)时,则VDA、VDB亦都正向导通,输出端F为低电平O(OV)。

当输入端一端为高电平,而另一端为低电平时,例如A端为3V,B端为OV。此时VDA管优先导通,输出端F被钳制在3V,使输出端F为高电平。同时VDB管受反向偏置而截止。

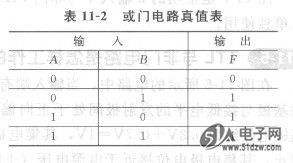

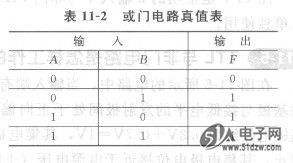

由上述可知,在或门电路的输入端中,只要有一端为高电平,输出端F就是高电平,只有输入端全为低电平时,输出端F才为低电平,即具有或逻辑关系。其真值表如表11-2所示。

由真值表可得出其逻辑表达式

F=A+B

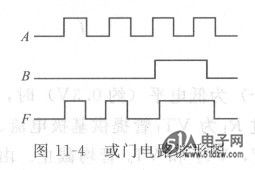

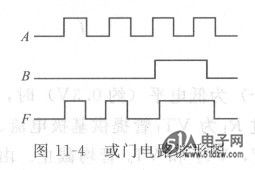

图11-4是或门电路的波形图。

(一)二极管与门电路是怎样工作的? G64128A09BBW00

图ll-l(a)是由二极管组成的与门电路,A、B是它的两个输入端,F是输出端。图(b)是它的逻辑符号。

设输入信号电压为3V(高电平1)或OV(低电平O),二极管为理想元件,则电路的工作原理如下。

当输入端A、B都为高电平1时,二极管VDA、VDB均处于正向导通状态,输出端F为高电平(3V)。

当输入端A、B都为低电平O时,二极管VDA、VDB亦处于正向导通状态,输出端F为低电平(OV)。

当输入端一端为高电平、另一端为低电平时,例如A端为3V,B端为OV,则VDB优先导通,输出端F被钳制在OV,输出为低电平。在VDB的钳位作用下,VDA处于截止状态。

由上述可知,与门电路的输入端中只要有一个为低电平,输出端就是低电平,只有输入端全为高电平时,输出端才是高电平。其真值表如表11―1所示。

由真值表可得出与门电路的逻辑表达式

F=A・B

(二)二极管或门电路是怎样工作的? R3111H601A-T1

图ll-3(a)是由二极管组成的或门电路,A、B为输入端,F是输出端。图(b)是或门的逻辑符号。工作原理分析如下。

当输入端A、B都处于高电平1(3V)时,则VDA、VDB都处于正向导通状态,输出端F为高电平1(3V)。

当输入端A、B都处于低电平O(OV)时,则VDA、VDB亦都正向导通,输出端F为低电平O(OV)。

当输入端一端为高电平,而另一端为低电平时,例如A端为3V,B端为OV。此时VDA管优先导通,输出端F被钳制在3V,使输出端F为高电平。同时VDB管受反向偏置而截止。

由上述可知,在或门电路的输入端中,只要有一端为高电平,输出端F就是高电平,只有输入端全为低电平时,输出端F才为低电平,即具有或逻辑关系。其真值表如表11-2所示。

由真值表可得出其逻辑表达式

F=A+B

图11-4是或门电路的波形图。

上一篇:模拟电路与数字电路基本原理

上一篇:TTL与非门电路工作状态与组成

公网安备44030402000607

公网安备44030402000607