触发点设置在43mA实现GHz带宽领域的高速信号采集

发布时间:2022/4/29 18:45:28 访问次数:240

DL9000采用横河电机的专利技术ADSE(Advanced Data Stream Engine),能够实现GHz带宽领域的高速信号采集和现实。

在高速采集模式下,采样内存最大可分割成1600个内存块,每次波形采集之后的死区时间(Dead Time)最大不超过400ns。即使是4通道同时采样,每通道的波形采集速度也可高达每秒钟250万个波形。

专用集成电路中的一种半定制电路,是可编程的逻辑阵列。FPGA的基本结构包括可编程输入输出单元、基本可编程逻辑单元、数字时钟管理模块、嵌入式块RAM、丰富的布线资源、内嵌专用硬核,以及底层内嵌功能单元。

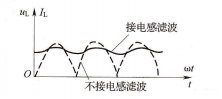

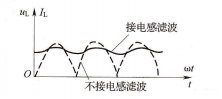

通道6上测量信号的电流探头和通道5上的RF输出,我们可以看到电流在周期性下跌。

匣查找B2682飞机左侧副翼调整片组件的件号。对该题进行分析副翼调整片组件应在27章。

在临时修订记录中,无记录信息。

在27章目录中找到AILERON AND TAB ASSY的条目,得到该组件图号27-11-2101。

找到27-11-2101图,进入详细零件清单,选取位置为LH副翼调整片,核对有效性,得到件号。

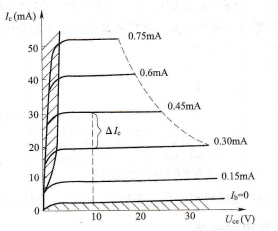

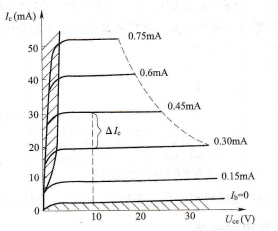

在时域中触发电流,而不是在频域中触发RF脉冲。为此,我们将把触发源变成通道6上的电流探头,因为我们知道正确操作发生在47mA,所以我们把触发点设置在43mA,在下降时捕捉信号。我们设置成触发电流边沿,而不是脉冲。

触发设置成捕获电流下降,以统一采集低电流情况。

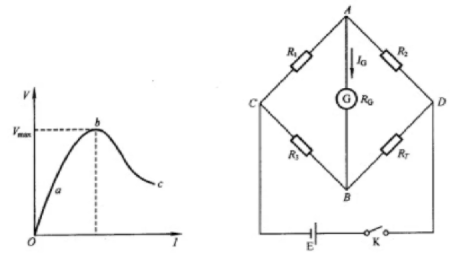

把RF下跌原因与示波器关联起来,在返回SignalVu时,我们现在可以捕捉电流开始下跌的时点。

在触发低电流情况时,我们在星座图中一直看到高EVM。

DL9000采用横河电机的专利技术ADSE(Advanced Data Stream Engine),能够实现GHz带宽领域的高速信号采集和现实。

在高速采集模式下,采样内存最大可分割成1600个内存块,每次波形采集之后的死区时间(Dead Time)最大不超过400ns。即使是4通道同时采样,每通道的波形采集速度也可高达每秒钟250万个波形。

专用集成电路中的一种半定制电路,是可编程的逻辑阵列。FPGA的基本结构包括可编程输入输出单元、基本可编程逻辑单元、数字时钟管理模块、嵌入式块RAM、丰富的布线资源、内嵌专用硬核,以及底层内嵌功能单元。

通道6上测量信号的电流探头和通道5上的RF输出,我们可以看到电流在周期性下跌。

匣查找B2682飞机左侧副翼调整片组件的件号。对该题进行分析副翼调整片组件应在27章。

在临时修订记录中,无记录信息。

在27章目录中找到AILERON AND TAB ASSY的条目,得到该组件图号27-11-2101。

找到27-11-2101图,进入详细零件清单,选取位置为LH副翼调整片,核对有效性,得到件号。

在时域中触发电流,而不是在频域中触发RF脉冲。为此,我们将把触发源变成通道6上的电流探头,因为我们知道正确操作发生在47mA,所以我们把触发点设置在43mA,在下降时捕捉信号。我们设置成触发电流边沿,而不是脉冲。

触发设置成捕获电流下降,以统一采集低电流情况。

把RF下跌原因与示波器关联起来,在返回SignalVu时,我们现在可以捕捉电流开始下跌的时点。

在触发低电流情况时,我们在星座图中一直看到高EVM。

公网安备44030402000607

公网安备44030402000607