储器进行数据处理100kHz的PWM和低至200ns的脉宽

发布时间:2022/2/8 13:04:58 访问次数:86

DRAM的3D键合堆叠存算一体AI芯片,可突破冯·诺依曼架构的性能瓶颈,满足人工智能等场景对高带宽、高容量内存和极致算力的需求。

在特定AI场景中,该芯片性能提升10倍以上,能效比提升高达300倍。

所谓“存算一体AI芯片”,是指将传统以计算为中心的架构转变为以数据为中心的架构,其直接利用存储器进行数据处理,从而把数据存储与计算融合在同一芯片中,极大提高计算并行度与能量效率,特别适用于深度学习神经网络领域,如可穿戴设备、移动设备、智能家居等场景。

它还包含2KB用户可访问的非易失性存储器。整个模块采用紧凑6.125” x 3.375” x 2.25”吋封装。

该控制器还有一个大范围的数字I/O电压。该数字I/O电压单纯采用软件技术,就能设置成3.3 V和27 V之间的任一电压.软件可配置的数字输入上拉电阻无需外接上拉电阻。

利用RRAM构建基于存算一体架构的深度学习神经网络(PRIME),受到业界的广泛关注。

测试结果表明,与基于冯·诺依曼计算架构的传统方案相比,PRIME可以实现功耗降低约20倍、速度提高约50倍。

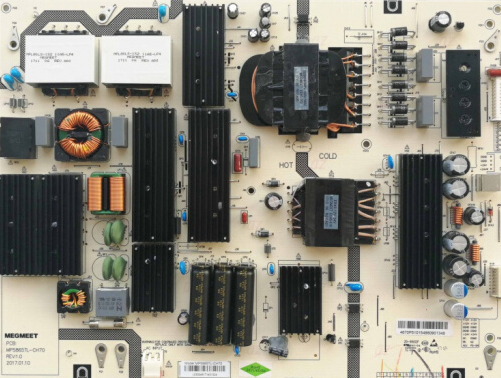

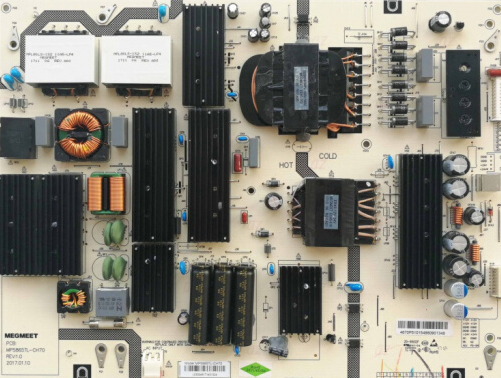

高速LED 驱动器支持高达100kHz的PWM和低至200ns的脉宽。该性能适合在25kHz频率级别实现1000:1调光范围,并且在该范围提供出色的直线性,支持非常细微的调光举措。

MC34845还采用升压转换器来产生所需电压,为LED供电。两种版本都可以用于600kHz (MC34845)或1.2MHz (MC34845A)的升压切换频率。

输入范围支持2节和3节锂电池或固定输入电源。高压输出性能让该器件能够驱动96个白色LED,驱动数量多于与之竞争的6信道设计。

(素材来源:转载自网络,如涉版权请联系删除,特别感谢)

DRAM的3D键合堆叠存算一体AI芯片,可突破冯·诺依曼架构的性能瓶颈,满足人工智能等场景对高带宽、高容量内存和极致算力的需求。

在特定AI场景中,该芯片性能提升10倍以上,能效比提升高达300倍。

所谓“存算一体AI芯片”,是指将传统以计算为中心的架构转变为以数据为中心的架构,其直接利用存储器进行数据处理,从而把数据存储与计算融合在同一芯片中,极大提高计算并行度与能量效率,特别适用于深度学习神经网络领域,如可穿戴设备、移动设备、智能家居等场景。

它还包含2KB用户可访问的非易失性存储器。整个模块采用紧凑6.125” x 3.375” x 2.25”吋封装。

该控制器还有一个大范围的数字I/O电压。该数字I/O电压单纯采用软件技术,就能设置成3.3 V和27 V之间的任一电压.软件可配置的数字输入上拉电阻无需外接上拉电阻。

利用RRAM构建基于存算一体架构的深度学习神经网络(PRIME),受到业界的广泛关注。

测试结果表明,与基于冯·诺依曼计算架构的传统方案相比,PRIME可以实现功耗降低约20倍、速度提高约50倍。

高速LED 驱动器支持高达100kHz的PWM和低至200ns的脉宽。该性能适合在25kHz频率级别实现1000:1调光范围,并且在该范围提供出色的直线性,支持非常细微的调光举措。

MC34845还采用升压转换器来产生所需电压,为LED供电。两种版本都可以用于600kHz (MC34845)或1.2MHz (MC34845A)的升压切换频率。

输入范围支持2节和3节锂电池或固定输入电源。高压输出性能让该器件能够驱动96个白色LED,驱动数量多于与之竞争的6信道设计。

(素材来源:转载自网络,如涉版权请联系删除,特别感谢)

公网安备44030402000607

公网安备44030402000607