W78L516A24DL GAL的基本结构

发布时间:2019/10/24 12:24:48 访问次数:974

W78L516A24DL级逻辑功能,并且具有更高的集成密度和应用灵活性。日前,超大规模的FPGA容量已达到百万个逻辑门以上,足以将现代CPU及其外围电路这样高度复杂的时序逻辑系统在单个芯片上编程实现。在软件上,亦有相应的操作系统配套。这样,可使整个数字系统(包括软、硬件系统)都在单个芯片上运行,即所谓的SOC①技术。

应用中,应根据实际的需求选择使用GAL、CPLD或FPGA等不同类型的SPLD。对于各种具体器件,一般都开发了计算机辅助设计工具,使它们能够通过硬件描述语言,例如ABEL、ⅤHDL和Verilog进行编程设计(对某种特定器件,有时会对某些语句有所限制),并可将目标码下载到芯片上实现硬件的编程。

本章将在6.7.3节讨论GAL的电路结构和工作原理,有关CPLD和FPGA的详细讨论将分别在7.3节和7.4节进行。

通用阵列逻辑GAL,GAL的基本结构,根据门阵列的结构,可以把现有的GAL器件分为两大类。其中一类GAL的组合逻辑部分与PAL器件基本相似,即与门阵列可编程,或门阵列固定连接,这类器件有GAL16V8,ispGAL16Z8②和GAL20V8等,称为通用型GAL;另一类GAL器件的与门阵列和或门阵列都可编程,GAL39V18属于这一类。通用型GAL中,GAL16V8有20个引脚,型号中的16表示最多能有16个引脚作为输入端,8表示器件内含8个0LMC,最多可有8个输出端。同理,GAL20V8最大可能的输人端个数是20,最多可有8个输出端。

下面以GAL16V8为例,说明GAL的电路结构和工作原理。图6,7.2所示为GAL16V8的逻辑结构图,它由五部分组成:

8个输人缓冲器(引脚2~9固定为输入端)。

8个输出缓冲器(引脚12~19为输出缓冲器的输出端)。

8个输出逻辑宏单元(0LMC12~19,或门阵列包含在其中)。

可编程与门阵列(由8×8个与门构成,形成64个乘积项,每个与门有32个输人端)。

8个输出反馈/输入缓冲器(图6.7.2中中问一列8个缓冲器)。

sOC系syslem On a Chip的缩写。

isp系in system programmability的缩写,该系列产品具有在线可编程功能.isp功能将在72节中介绍.

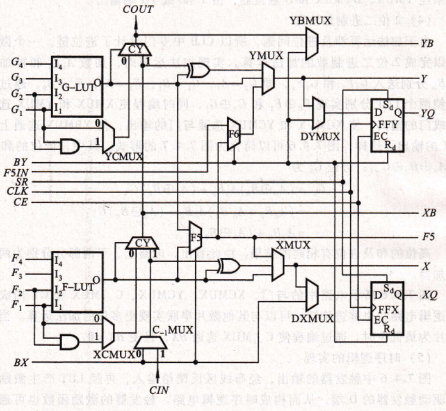

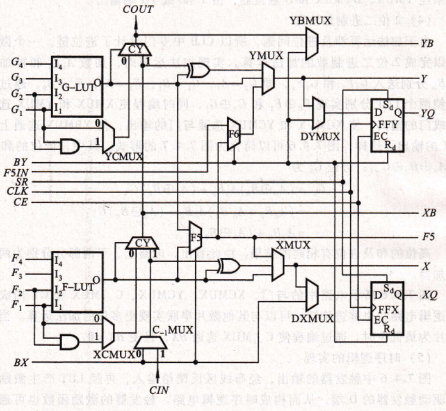

来自CLB以外布线区的4个输入变量同时送人F1~F4和相应的C1~C4,第5个输入变量送至BX端。F-LUT、G-LUT的输出和BX经数据选择器F5扩展为5变量逻辑函数。该结果可直接由F5端输出,也可经XMUX、DXMUX和D触发器,由X和/或X0端输出。

实现6变量任意逻辑函数,实现6变量任意逻辑函数需用2个微片。在实现5变量函数基础上,将另一个微片的乃的输出送入此微片的F5JⅣ输人端,第6个变量送人By端。数据选择器F5的输出、F5JⅣ和By经数据选择器F6扩展为6变量逻辑函数。该结果经YMUX、DYMUX和D触发器,由y和/或yQ端输出。

2位二进制加法器,由于加法运算涉及进位问题,所以CLB中专门设计了进位链,一个微片可以完成2位二进制数的加法运算。实现加法运算时,加数A1A。和被加数B1BO分别送入G2F2和G1F1,即C2=A1,Cl=B1,F2=A。,F1=BO。通过编程使两个LUT分别实现F2①F1和C2①C1,同时编程使XMUx和YMUX选通异或门的输出,使xCMUX和YCMUX选通与门的输出,使YBMUX选通上端CY的输出。这样,图7.4,6可以简化为图7.4.7的形式。其中,低位的和S。=A0①BO①Ci,进位C。为

C0=(A0①B0)AOBO+(A0①BO)C~1

=(AOB0+AO BO)AOBO+(A0①B0)C~1

=A0BO+(A0∈)B0)C~1

高位的和及进位有相同的结果,由此看出,电路上、下两部分分别为两个全加器。

图7.4.6所示电路中的与门、ⅩCMUX、YCMUX、C~1^MUX和CY构成进位逻辑电路,也称进位链,可以与其他微片串联实现更多位的加法运算。当此微片为最低位时,通过编程使C~1MUX选通BX,且使Bx二0。

时序逻辑的实现,图7.4,6中触发器的输出,经布线区反馈给输人,再经LUT产生激励函数驱动触发器的D端,从而构成时序逻辑电路。触发器的激励函数也可通过

DXMUX(DYMUX)直接取自BX(By)。由多个CLB便可构成复杂的时序逻辑电路。

由于LUT就是一个16×1位的SRAM,所以CLB也可用来作存储器使用,不过此时LUT中的内容不再是预先配置好的,而是在正常工作时可以随时读写的,而且LUT不能再作为逻辑函数产生器使用。LUT也可以被设置成16位移位寄存器使用。另外,为弥补LUT构成RAM在容量上的不足,在FPGA中还增加了RAM块。这些RAM块以列的形式排列.

W78L516A24DL级逻辑功能,并且具有更高的集成密度和应用灵活性。日前,超大规模的FPGA容量已达到百万个逻辑门以上,足以将现代CPU及其外围电路这样高度复杂的时序逻辑系统在单个芯片上编程实现。在软件上,亦有相应的操作系统配套。这样,可使整个数字系统(包括软、硬件系统)都在单个芯片上运行,即所谓的SOC①技术。

应用中,应根据实际的需求选择使用GAL、CPLD或FPGA等不同类型的SPLD。对于各种具体器件,一般都开发了计算机辅助设计工具,使它们能够通过硬件描述语言,例如ABEL、ⅤHDL和Verilog进行编程设计(对某种特定器件,有时会对某些语句有所限制),并可将目标码下载到芯片上实现硬件的编程。

本章将在6.7.3节讨论GAL的电路结构和工作原理,有关CPLD和FPGA的详细讨论将分别在7.3节和7.4节进行。

通用阵列逻辑GAL,GAL的基本结构,根据门阵列的结构,可以把现有的GAL器件分为两大类。其中一类GAL的组合逻辑部分与PAL器件基本相似,即与门阵列可编程,或门阵列固定连接,这类器件有GAL16V8,ispGAL16Z8②和GAL20V8等,称为通用型GAL;另一类GAL器件的与门阵列和或门阵列都可编程,GAL39V18属于这一类。通用型GAL中,GAL16V8有20个引脚,型号中的16表示最多能有16个引脚作为输入端,8表示器件内含8个0LMC,最多可有8个输出端。同理,GAL20V8最大可能的输人端个数是20,最多可有8个输出端。

下面以GAL16V8为例,说明GAL的电路结构和工作原理。图6,7.2所示为GAL16V8的逻辑结构图,它由五部分组成:

8个输人缓冲器(引脚2~9固定为输入端)。

8个输出缓冲器(引脚12~19为输出缓冲器的输出端)。

8个输出逻辑宏单元(0LMC12~19,或门阵列包含在其中)。

可编程与门阵列(由8×8个与门构成,形成64个乘积项,每个与门有32个输人端)。

8个输出反馈/输入缓冲器(图6.7.2中中问一列8个缓冲器)。

sOC系syslem On a Chip的缩写。

isp系in system programmability的缩写,该系列产品具有在线可编程功能.isp功能将在72节中介绍.

来自CLB以外布线区的4个输入变量同时送人F1~F4和相应的C1~C4,第5个输入变量送至BX端。F-LUT、G-LUT的输出和BX经数据选择器F5扩展为5变量逻辑函数。该结果可直接由F5端输出,也可经XMUX、DXMUX和D触发器,由X和/或X0端输出。

实现6变量任意逻辑函数,实现6变量任意逻辑函数需用2个微片。在实现5变量函数基础上,将另一个微片的乃的输出送入此微片的F5JⅣ输人端,第6个变量送人By端。数据选择器F5的输出、F5JⅣ和By经数据选择器F6扩展为6变量逻辑函数。该结果经YMUX、DYMUX和D触发器,由y和/或yQ端输出。

2位二进制加法器,由于加法运算涉及进位问题,所以CLB中专门设计了进位链,一个微片可以完成2位二进制数的加法运算。实现加法运算时,加数A1A。和被加数B1BO分别送入G2F2和G1F1,即C2=A1,Cl=B1,F2=A。,F1=BO。通过编程使两个LUT分别实现F2①F1和C2①C1,同时编程使XMUx和YMUX选通异或门的输出,使xCMUX和YCMUX选通与门的输出,使YBMUX选通上端CY的输出。这样,图7.4,6可以简化为图7.4.7的形式。其中,低位的和S。=A0①BO①Ci,进位C。为

C0=(A0①B0)AOBO+(A0①BO)C~1

=(AOB0+AO BO)AOBO+(A0①B0)C~1

=A0BO+(A0∈)B0)C~1

高位的和及进位有相同的结果,由此看出,电路上、下两部分分别为两个全加器。

图7.4.6所示电路中的与门、ⅩCMUX、YCMUX、C~1^MUX和CY构成进位逻辑电路,也称进位链,可以与其他微片串联实现更多位的加法运算。当此微片为最低位时,通过编程使C~1MUX选通BX,且使Bx二0。

时序逻辑的实现,图7.4,6中触发器的输出,经布线区反馈给输人,再经LUT产生激励函数驱动触发器的D端,从而构成时序逻辑电路。触发器的激励函数也可通过

DXMUX(DYMUX)直接取自BX(By)。由多个CLB便可构成复杂的时序逻辑电路。

由于LUT就是一个16×1位的SRAM,所以CLB也可用来作存储器使用,不过此时LUT中的内容不再是预先配置好的,而是在正常工作时可以随时读写的,而且LUT不能再作为逻辑函数产生器使用。LUT也可以被设置成16位移位寄存器使用。另外,为弥补LUT构成RAM在容量上的不足,在FPGA中还增加了RAM块。这些RAM块以列的形式排列.

上一篇:STM8319 整形及定时

公网安备44030402000607

公网安备44030402000607