SI-81506Z 逻辑功能分析

发布时间:2019/10/17 17:34:24 访问次数:728

SI-81506Z观察状态图和时序图可知,图6.2.1所示的电路是一个由信号A控制的可控二进制计数器,CP为计数脉冲。当4=0时停止计数,电路状态保持不变:当A=1时,在CP上升沿到来后电路状态值加1,一旦计数到11状态,y输出1,且电路状态将在下一个CP上升沿回到00。输出信号y的下降沿可用于触发进位操作。观察图6.2.3所示的时序图,在第9个和第10个CP脉冲之间,输入信号且出现短时间的0电平,如图6,2.3中箭头①所示,结果使输出y也出现相应变化。倘若信号且上这个低电平脉冲是外界干扰造成的(输入信号引线有时较长,易捡拾干扰信号),计数器将输出两次进位触发脉冲沿,如图6,2.3中箭头②所示。在本节末尾将讨论如何改进电路,以尽量避免发生错误的逻辑输出。

该电路亦可作为序列信号检测器,用来检测同步脉冲信号序列A中1的个数,一旦检测到四个1状态(这四个1状态可以不连续),电路则输出高电平。

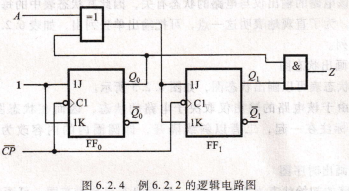

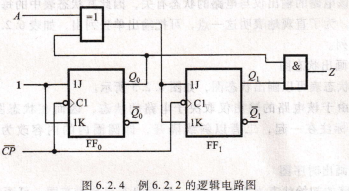

例6.2,2 分析图6.2,4所示同步时序电路。

解:这是一个由两个下降沿触发的JK触发器、一个异或门及一个与门组成的时序电路。

根据电路列出三个方程组

输出方程组

z=q1q0

激励方程组

j0=k1=a+q0

Jl=K1=A+q0

状态方程组,将两个激励方程分别代入JK触发器的特性方程,得到两个触发器的状态方程

qn+1=JOq0+K0q0=0

Qn+1=J101+K10:

=(A+Q:)Q1+A+Q0Q1

=A+Q+Q1

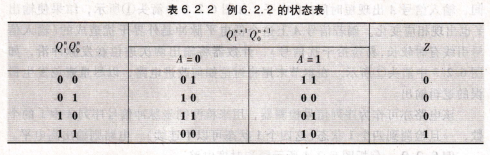

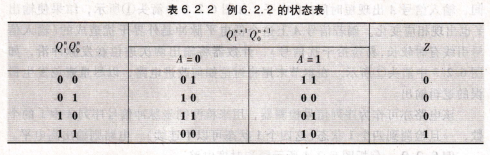

表6.2.2 例6.2.2的状态表由于该电路的输出仅与电路的状态有关,因定的输出。为了直观地表明这一点,可把输出号z的一列。

SI-81506Z观察状态图和时序图可知,图6.2.1所示的电路是一个由信号A控制的可控二进制计数器,CP为计数脉冲。当4=0时停止计数,电路状态保持不变:当A=1时,在CP上升沿到来后电路状态值加1,一旦计数到11状态,y输出1,且电路状态将在下一个CP上升沿回到00。输出信号y的下降沿可用于触发进位操作。观察图6.2.3所示的时序图,在第9个和第10个CP脉冲之间,输入信号且出现短时间的0电平,如图6,2.3中箭头①所示,结果使输出y也出现相应变化。倘若信号且上这个低电平脉冲是外界干扰造成的(输入信号引线有时较长,易捡拾干扰信号),计数器将输出两次进位触发脉冲沿,如图6,2.3中箭头②所示。在本节末尾将讨论如何改进电路,以尽量避免发生错误的逻辑输出。

该电路亦可作为序列信号检测器,用来检测同步脉冲信号序列A中1的个数,一旦检测到四个1状态(这四个1状态可以不连续),电路则输出高电平。

例6.2,2 分析图6.2,4所示同步时序电路。

解:这是一个由两个下降沿触发的JK触发器、一个异或门及一个与门组成的时序电路。

根据电路列出三个方程组

输出方程组

z=q1q0

激励方程组

j0=k1=a+q0

Jl=K1=A+q0

状态方程组,将两个激励方程分别代入JK触发器的特性方程,得到两个触发器的状态方程

qn+1=JOq0+K0q0=0

Qn+1=J101+K10:

=(A+Q:)Q1+A+Q0Q1

=A+Q+Q1

表6.2.2 例6.2.2的状态表由于该电路的输出仅与电路的状态有关,因定的输出。为了直观地表明这一点,可把输出号z的一列。

公网安备44030402000607

公网安备44030402000607