SOPCϵͳ���ʵ��

����ʱ��:2018/3/3 20:04:18 ���ʴ���:601

A1tc�¡�os����һ������FPGA�����Ŀ����Ƶ�CPUϵͳ,����ʱ��������ı䶯,ͨ��soPC B��ldcrƽ̨���ж��Ʋü�,�������IP�����Ի�����Ӧ,�õ������SoPC(s��temon a Programmablc Chip)ʽ��CPUϵͳ�� SN65ALS180DR

������soPC��Ӳ�����¿��Է�Ϊ3������:FPGA���֡��洢�����ֺ���ΧԪ�����֡�FPGA���ְ������û����Ƶ�:����һ��Nios �� RIsC�������ںˡ�Ƭ�ڿɱ�̸���RAM��Դ�����غ����Գ����JTAG UARTͨ��ģ�顢�ڲ���ʱ����Avolon���߿�������PIo�ӿڿ顢���ܰ������ֵĿɱ��ģ���·��Ϊʹ��osϵͳ��������,��FPGA��Χ�������Ĵ洢�����֡���ΧԪ��������ʱ���ź�Դ�����밴�����˻��ӿڵ�·�������ʾ�豸�ȡ�

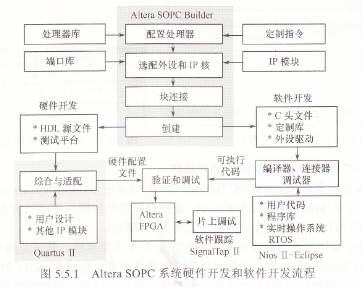

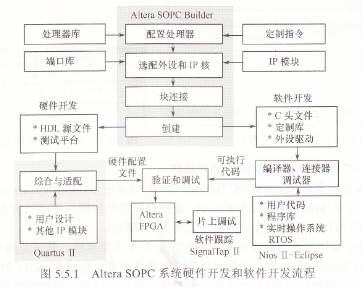

A1tera soPCϵͳ������̴�����:ϵͳ������Ӳ����ơ��������Эͬ��֤����ԡ��ֿ��Է�ΪӲ������������������������,��ͼ5.5.1��ʾ��Ӳ������������Ҫ���û�����ϵͳӲ��,��Quartus ��ƽ̨�µ�soPC B֤lder�������ϵͳӲ���Ͷ�Ӧ�Ŀ������������ɡ�QuartLIs II ��120��Nios �� Eclipse�ǽ���SOPC������������ơ����Ժ����еĹ���,��ͼ�λ����������ɿ�������(�ɰ汾��Nios �� IDE,������������)��

A1tc�¡�os����һ������FPGA�����Ŀ����Ƶ�CPUϵͳ,����ʱ��������ı䶯,ͨ��soPC B��ldcrƽ̨���ж��Ʋü�,�������IP�����Ի�����Ӧ,�õ������SoPC(s��temon a Programmablc Chip)ʽ��CPUϵͳ�� SN65ALS180DR

������soPC��Ӳ�����¿��Է�Ϊ3������:FPGA���֡��洢�����ֺ���ΧԪ�����֡�FPGA���ְ������û����Ƶ�:����һ��Nios �� RIsC�������ںˡ�Ƭ�ڿɱ�̸���RAM��Դ�����غ����Գ����JTAG UARTͨ��ģ�顢�ڲ���ʱ����Avolon���߿�������PIo�ӿڿ顢���ܰ������ֵĿɱ��ģ���·��Ϊʹ��osϵͳ��������,��FPGA��Χ�������Ĵ洢�����֡���ΧԪ��������ʱ���ź�Դ�����밴�����˻��ӿڵ�·�������ʾ�豸�ȡ�

A1tera soPCϵͳ������̴�����:ϵͳ������Ӳ����ơ��������Эͬ��֤����ԡ��ֿ��Է�ΪӲ������������������������,��ͼ5.5.1��ʾ��Ӳ������������Ҫ���û�����ϵͳӲ��,��Quartus ��ƽ̨�µ�soPC B֤lder�������ϵͳӲ���Ͷ�Ӧ�Ŀ������������ɡ�QuartLIs II ��120��Nios �� Eclipse�ǽ���SOPC������������ơ����Ժ����еĹ���,��ͼ�λ����������ɿ�������(�ɰ汾��Nios �� IDE,������������)��

��һƪ���Ʒ�ģ��

��һƪ��Ӳ�����������

�������

�������

- ���õ�7��������:

- ��ȷϵͳ����������Ҫ��

- ˫���;����������PN�ṹ��

- ������Ӿ����(AVI)

- ����ķ���(������)��Ҫ����������

- Ŀǰ�кܶ��ֶ���̽�����

- ��Ƶ�Ĵ����Կ��ŶȲ���ͨ���Բ�ģΪ��

- �̿�����Ŵ����������Ӧ��

- ˫��Դ������Ƶ�·

- ��̬�������Ӱ��

�Ƽ���������

�Ƽ���������

- ѭ�������ǻ��������ź�

- ѭ�������ǻ��������źͱ�����õĿ��Ʒ�ʽ��E48S... [��ϸ]

- MOSFET ��е�Ƭ��ѹ����ģʽ�任������

- SiC MOSFET �� IG

- ���� �������о���Ի���ЧӦ��

- ҵ�糬С����λ�ñ����������������

- �ߴ��������߷ֱ��ʴŽǶȴ��м���Ӧ��̽��

- MagAlpha �Ƕ�λ�ô���

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607