�ݰ������еĸ���ԭ������,�����ģ���ŵ�ѹ

����ʱ��:2017/6/27 21:14:46 ���ʴ���:447

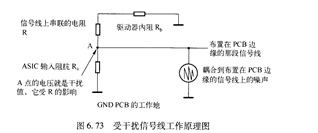

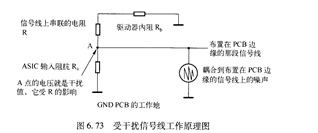

���ڸ��ź����нϳ���һ���߲�����PCB��Ե,�����β�����PCB��Ե���ź�����ʰȡ�� OG-320816�ⲿע�˵���Ʒ�еĹ�ģ����,��ת��Ϊ��ģ����(��AsIC�ź����˶˿���ASIC������֮��ĸ���,����ԭ���������ʷ���)�����ݰ������еĸ���ԭ������,�����ģ���ŵ�ѹ(ͼ6.73��A��ĵ�ѹ)������ӡ���ߺͲο��ӵذ�֮��ļ������ݴ�С�й�,����AsIC�źŶ˿ں��乤����֮����迹�й�,��ASIC�źŶ˿����乤����֮����迹��ͼ6.73�е�Ra,R,Rb���й�ϵ,����R,Rb��������Ra�����Ľ��,Ra�Ǹ��ϴ��һ��ֵ,��k����,��Rb�Ǹ���С��ֵ,����R�Ĵ�Сֱ�Ӿ�����A��ĵ�ѹ����R��1k����Ϊ100��ʱ,A��ĸ��ŵ�ѹҲ�����(��ԭ������Լ90%),���Բ���ͨ����

��������ʩ��

�����Ϸ���,�Ѳ�����PCB��Ե���ź����Ƶ�PCB�ڲ�,���ź����ϵĴ��������1k����Ϊ100����

��˼������ʾ��

(1)��Ҫ����·�е������߲�����PCB��Ե;

(2)оƬ�źŶ˿����ܵĸ�����оƬ�źŶ˿ڵ������迹�й�,�������迹��оƬ�ź��˿ڸ������ܸ���Ӱ�졣���,�ڵ�·�����,Ҫ�ž�δ�õ�оƬ�źŶ˿�����(�ر����������迹��оƬ�˿�,��CMOs����������˿�),��Ҫ��ͨ�����迹�ӹ����ء�

���ڸ��ź����нϳ���һ���߲�����PCB��Ե,�����β�����PCB��Ե���ź�����ʰȡ�� OG-320816�ⲿע�˵���Ʒ�еĹ�ģ����,��ת��Ϊ��ģ����(��AsIC�ź����˶˿���ASIC������֮��ĸ���,����ԭ���������ʷ���)�����ݰ������еĸ���ԭ������,�����ģ���ŵ�ѹ(ͼ6.73��A��ĵ�ѹ)������ӡ���ߺͲο��ӵذ�֮��ļ������ݴ�С�й�,����AsIC�źŶ˿ں��乤����֮����迹�й�,��ASIC�źŶ˿����乤����֮����迹��ͼ6.73�е�Ra,R,Rb���й�ϵ,����R,Rb��������Ra�����Ľ��,Ra�Ǹ��ϴ��һ��ֵ,��k����,��Rb�Ǹ���С��ֵ,����R�Ĵ�Сֱ�Ӿ�����A��ĵ�ѹ����R��1k����Ϊ100��ʱ,A��ĸ��ŵ�ѹҲ�����(��ԭ������Լ90%),���Բ���ͨ����

��������ʩ��

�����Ϸ���,�Ѳ�����PCB��Ե���ź����Ƶ�PCB�ڲ�,���ź����ϵĴ��������1k����Ϊ100����

��˼������ʾ��

(1)��Ҫ����·�е������߲�����PCB��Ե;

(2)оƬ�źŶ˿����ܵĸ�����оƬ�źŶ˿ڵ������迹�й�,�������迹��оƬ�ź��˿ڸ������ܸ���Ӱ�졣���,�ڵ�·�����,Ҫ�ž�δ�õ�оƬ�źŶ˿�����(�ر����������迹��оƬ�˿�,��CMOs����������˿�),��Ҫ��ͨ�����迹�ӹ����ء�

��һƪ���ź�����PCB�еIJ������

�������

�������

- ���������ʪ����ʴ

- �ٵĿ�ʴ

- ������ĸɷ���ʴ

- �����Ʊ�

- оƬ��������

- ��ƽ�е���֮��ľ������������ݵ�Ӱ��

- Ŀǰ�г��ϳ��ֵ�BGA��װ,�����������

- WLR�D�D��Ƭ���ɿ��Բ���

- ��������̽�

- ��̹��ն���ģ�������Ҫ�����

�Ƽ���������

�Ƽ���������

- ҵ��������PCM2702

- PGM2702����SSOP28��װ������С���ܣ�EP3... [��ϸ]

��������44030402000607

��������44030402000607