非本征器件

发布时间:2013/7/29 20:33:31 访问次数:1216

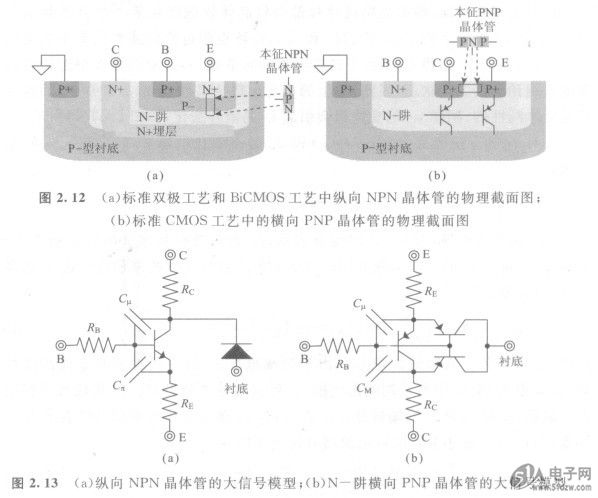

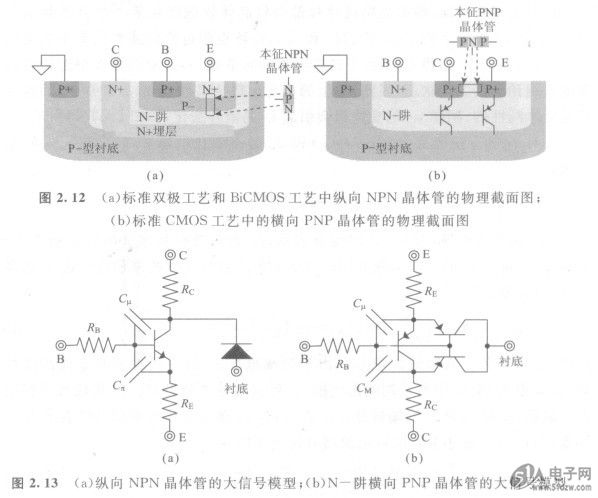

本征器件表面上是两个背靠背的PN结结合在一起,PCF8566T而不是扩散和用于连接器件的接触孔(图2.12)。每个端口的欧姆接触串联电阻及其相应的寄生PN结形成了双极型晶体管的非本征部分。如图2.12所示,大信号和小信号模型中都包含了基区串联电阻RH、发射极电阻RE、集电极电阻R类似地,图2.13 (a)也包含了反向偏置的集电极一衬底PN结二极管及其等效寄生电容。

图2.12 (a)标准双极工艺和BiCMOS工艺中纵向NPN晶体管的物理截面图

(b)标准CMOSI艺中的横向PNP晶体管的物理截面图

图2.13 (a)纵向NPN晶体管的大信号模型;(b)N一阱横向PNP晶体管的大信号模型

N-阱横向PNP也有两个寄生的双极型PNP晶体管,这两个寄生晶体管与横向PNP晶体管共用同一个基区,并且通过衬底连接到地电压[图2.12 (b)和图2.13(b)。由于发射极是高电势,其各自的寄生晶体管会引发更多的问题,会降低横向晶体管的整体电流效率。如果工艺允许,通过在N-阱上增加N+埋层,可以提高载流子复合概率,从而降低这些寄生晶体管的增益。

图2.12 (a)所示的标准双极工艺或者BiCMOS工艺中纵向NPN晶体管增加的埋层可以降低集电极的寄生串联电阻。如果没有这一层,由于本征晶体管的集电极处于衬底很深的位置,距离外部表面接触孔较远,当外部集电极一发射极电压vCI进一步增大时,器件进入饱和区,这是因为晶体管上真正的VCE由于Rc:欧姆压降的存在而降低了。由于发射极接触靠近外部即芯片表面接触点,因此正常情况下,发射极电阻都比较低。图2.12(b)所示的标准CMOS工艺中横向PNP晶体管集电极电阻较低,这是因为真正的集电极靠近其外部的接触孔。但是,负面效果是相对于优化设计后的纵向器件,由于其基区掺杂浓度低,则基区电阻变大,会有更为显著的基区宽度调制效应(即厄尔利电压VA更小,或者说等效输出电阻变小),当反向偏置电压改变时,低掺杂就会导致耗尽区宽度变化更为显著。

本征器件表面上是两个背靠背的PN结结合在一起,PCF8566T而不是扩散和用于连接器件的接触孔(图2.12)。每个端口的欧姆接触串联电阻及其相应的寄生PN结形成了双极型晶体管的非本征部分。如图2.12所示,大信号和小信号模型中都包含了基区串联电阻RH、发射极电阻RE、集电极电阻R类似地,图2.13 (a)也包含了反向偏置的集电极一衬底PN结二极管及其等效寄生电容。

图2.12 (a)标准双极工艺和BiCMOS工艺中纵向NPN晶体管的物理截面图

(b)标准CMOSI艺中的横向PNP晶体管的物理截面图

图2.13 (a)纵向NPN晶体管的大信号模型;(b)N一阱横向PNP晶体管的大信号模型

N-阱横向PNP也有两个寄生的双极型PNP晶体管,这两个寄生晶体管与横向PNP晶体管共用同一个基区,并且通过衬底连接到地电压[图2.12 (b)和图2.13(b)。由于发射极是高电势,其各自的寄生晶体管会引发更多的问题,会降低横向晶体管的整体电流效率。如果工艺允许,通过在N-阱上增加N+埋层,可以提高载流子复合概率,从而降低这些寄生晶体管的增益。

图2.12 (a)所示的标准双极工艺或者BiCMOS工艺中纵向NPN晶体管增加的埋层可以降低集电极的寄生串联电阻。如果没有这一层,由于本征晶体管的集电极处于衬底很深的位置,距离外部表面接触孔较远,当外部集电极一发射极电压vCI进一步增大时,器件进入饱和区,这是因为晶体管上真正的VCE由于Rc:欧姆压降的存在而降低了。由于发射极接触靠近外部即芯片表面接触点,因此正常情况下,发射极电阻都比较低。图2.12(b)所示的标准CMOS工艺中横向PNP晶体管集电极电阻较低,这是因为真正的集电极靠近其外部的接触孔。但是,负面效果是相对于优化设计后的纵向器件,由于其基区掺杂浓度低,则基区电阻变大,会有更为显著的基区宽度调制效应(即厄尔利电压VA更小,或者说等效输出电阻变小),当反向偏置电压改变时,低掺杂就会导致耗尽区宽度变化更为显著。

上一篇:NPN双极型晶体管的符号

热门点击

热门点击

- 直流偏置

- 电阻将电能转化为热能

- 双管推挽式振荡器电路

- 输出级的寄生振荡及栅极抑振电阻

- 电感器的谐振功能

- 级联式恒流源及其面对市电变动时的稳定度

- 晶体三极管在电路中的基本功能

- 差分对电路的增益

- 远用电子表格软件进行音量衰减器的计算

- 非本征器件

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607