一位数比较器

发布时间:2012/12/8 19:44:10 访问次数:1532

比较器有一位数码比较器和多EPM7128BTC100-10位数码比较器两种,前者只能对一位二进制数进行比较,后都则能对多位二进制数进行比较。

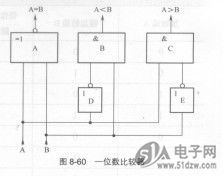

图8-60所示是由5个逻辑门构成的一位数比较器。电路中,逻辑门A是一个异或非门,逻辑门B和C是具有两个输入端的与门电路,逻辑门D和E是非门电路,输入端A和B是参与比较的两个一位的二进制数码,这一比较器电路有3个输出端,即A>B,A<B,A=B,这是因为两个数相比较可能有3种不同的结果。

工作原理

多位数比较器的工作原理要分成下列3种情况进行分析。

第一种情况是这样:首先比较高位,如果某一多位数A的最高位比另一个多位数B的最高位大,此时无论这两个多位数的其他位数情况如何,多位数A肯定大于多位数B,此多位数比较器就是A>B输出端输出1,这表示A数大于B数。

第二种情况是这样:首先比较高位,如果某一多位数B的最高位比另一个多位数A的最高位大,此时无论这两个多位数的其他位数情况如何,多位数B肯定大于多位数A,此多位数比较器就是B>A输出端输出1,这表示B数大于A数。

第三种情况是这样:如果A、B数的最高位比较结果是相等,那么进行两数的次高位数比较,比较的结果哪个数大就是哪个数大,若比较的结果仍然是相等,那么再进行下一位数的比较,直到最后一位数比较的结果都是相等时,多位数比较器的A=B输出端输出1.这说明多位数A等于多位数B。

比较器有一位数码比较器和多EPM7128BTC100-10位数码比较器两种,前者只能对一位二进制数进行比较,后都则能对多位二进制数进行比较。

图8-60所示是由5个逻辑门构成的一位数比较器。电路中,逻辑门A是一个异或非门,逻辑门B和C是具有两个输入端的与门电路,逻辑门D和E是非门电路,输入端A和B是参与比较的两个一位的二进制数码,这一比较器电路有3个输出端,即A>B,A<B,A=B,这是因为两个数相比较可能有3种不同的结果。

工作原理

多位数比较器的工作原理要分成下列3种情况进行分析。

第一种情况是这样:首先比较高位,如果某一多位数A的最高位比另一个多位数B的最高位大,此时无论这两个多位数的其他位数情况如何,多位数A肯定大于多位数B,此多位数比较器就是A>B输出端输出1,这表示A数大于B数。

第二种情况是这样:首先比较高位,如果某一多位数B的最高位比另一个多位数A的最高位大,此时无论这两个多位数的其他位数情况如何,多位数B肯定大于多位数A,此多位数比较器就是B>A输出端输出1,这表示B数大于A数。

第三种情况是这样:如果A、B数的最高位比较结果是相等,那么进行两数的次高位数比较,比较的结果哪个数大就是哪个数大,若比较的结果仍然是相等,那么再进行下一位数的比较,直到最后一位数比较的结果都是相等时,多位数比较器的A=B输出端输出1.这说明多位数A等于多位数B。

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607