利用I/O引脚为外部器件供电

发布时间:2012/2/18 18:12:52 访问次数:866

在嵌入式系统中,SDRAM常用做数据存储器。如果微处理器的本地总线频率为66~100MH。(如MPC8270),采用SDR SDRAM(单数据率同步动态随机存储器)的存储容量和速度均能满足要求,如MT48LC2M3282。 IC0603A103R-10

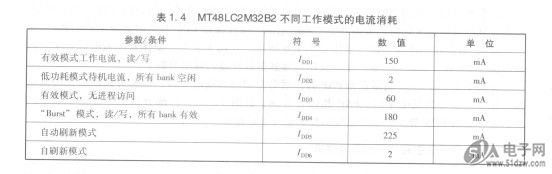

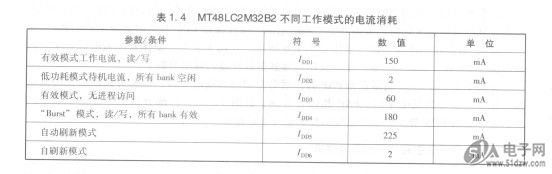

SDR SDRAM存储器芯片的有效工作电流可以达到几百mA,见表1.4,MT48LC2M3282的有效工作电流为150mA,自动刷新模式电流为225 mA,而低功耗待机模式电流仅为2mA。设计时应控制存储器芯片仅在数据读/写时才有效(片选信号有效),一旦读/写完成,即刻使片选信号无效,存储器芯片便处于低功耗的数据保持状态。

针对SDR SDRAM的低功耗设计,可以采取如下措施:

・低电压供电,如3. 3V。

・在能够满足系统要求的情况下,尽量选择单片存储器。

・存储器芯片直接焊接在电路板上,而不使用内存条的方式。

・采用低功耗的Power-Down模式。

・采用低功耗的Self-Refresh Mode(自刷新模式)。

在嵌入式系统中,SDRAM常用做数据存储器。如果微处理器的本地总线频率为66~100MH。(如MPC8270),采用SDR SDRAM(单数据率同步动态随机存储器)的存储容量和速度均能满足要求,如MT48LC2M3282。 IC0603A103R-10

SDR SDRAM存储器芯片的有效工作电流可以达到几百mA,见表1.4,MT48LC2M3282的有效工作电流为150mA,自动刷新模式电流为225 mA,而低功耗待机模式电流仅为2mA。设计时应控制存储器芯片仅在数据读/写时才有效(片选信号有效),一旦读/写完成,即刻使片选信号无效,存储器芯片便处于低功耗的数据保持状态。

针对SDR SDRAM的低功耗设计,可以采取如下措施:

・低电压供电,如3. 3V。

・在能够满足系统要求的情况下,尽量选择单片存储器。

・存储器芯片直接焊接在电路板上,而不使用内存条的方式。

・采用低功耗的Power-Down模式。

・采用低功耗的Self-Refresh Mode(自刷新模式)。

热门点击

热门点击

- 三极管电路图形符号

- 稳压二极管结构和工作原理

- 三极管的电流放大作用

- 倒T形电阻网络DAC

- 变压器常用参数及参数识别方法

- 用555定时器组成的多谐振荡器

- 桥堆构成的整流电路

- 研究负反馈对放大电路性能的影响

- 三端可调输出集成稳压器

- RC低频提升电路

推荐技术资料

推荐技术资料

- DFRobot―玩的就是

- 如果说新车间的特点是“灵动”,FQPF12N60C那么... [详细]

公网安备44030402000607

公网安备44030402000607