组合逻辑电路的设计

发布时间:2012/2/14 21:36:34 访问次数:1197

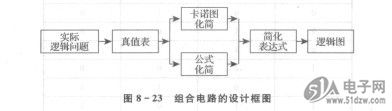

组合逻辑的设计,就是根据给定的逻辑关系,求出实现这一逻辑关系的最简逻辑电路图,组合电路的一般设计过程粗略地归纳为四个基本步骤,如图8 - 23所示。QP37256P160-83UMB

设计组合逻辑电路步骤如下:

(1)分析要求

首先,根据给定的设计要求(设计要求可以是一段文字说明,或者是一个具体的逻辑问题,也可能是一张功能表等),分析其逻辑关系,确定哪些是输入变量,哪些是输出函数,以及它们之间的相互关系。然后,用0、1表示输入变量和输出函数的响应状态,称为状态赋值。

(2)列真值表

根据上述分析和赋值情况,将输入变量的所有取值组合和与之相对应的输出函数值列表,即得真值表。注意,不会出现或不允许出现的输入变量取值组合可以不列出,如果列出,可在相应的输出函数处记上“×”号,化简时可作约束项处理。

(3)化简

用卡诺图法或公式法进行化简,得到最简逻辑函数表达式。

(4)画逻辑图

根据简化后的逻辑表达式画出逻辑电路图。如果对采用的门电路类型有要求,可遁当变换表达式形式(如与非、或非、与或非表达式等),然后用对应的门电路构成逻辑图。

设计举例:

例8-2试设计一个3人投票表决器,即3人中有2人或3人表示同意,则表决通过;否则为不通过。

解:首先,进行逻辑抽象。关键:

①弄清楚哪些是输入变量,哪些是输出变量;

②弄清楚输入变量与输出变量间的因果关系;

. ③对输入、输出变量进行状态赋值。

A、B、C是否同意为输入信号,决议是否通过为输出信号。设输入A(或B、C)为1表示同意,为O表示不同意;输出y为1表示决议通过,为O表示决议不通过。

第一步:确定输入、输出变量。

设A,B,C分别代表三人表决的逻辑变量。y代表表决的结果。

第二步:定义逻辑状态的含义。

设A,B,C为1表示赞成;O表示反对(反之亦然)。

组合逻辑的设计,就是根据给定的逻辑关系,求出实现这一逻辑关系的最简逻辑电路图,组合电路的一般设计过程粗略地归纳为四个基本步骤,如图8 - 23所示。QP37256P160-83UMB

设计组合逻辑电路步骤如下:

(1)分析要求

首先,根据给定的设计要求(设计要求可以是一段文字说明,或者是一个具体的逻辑问题,也可能是一张功能表等),分析其逻辑关系,确定哪些是输入变量,哪些是输出函数,以及它们之间的相互关系。然后,用0、1表示输入变量和输出函数的响应状态,称为状态赋值。

(2)列真值表

根据上述分析和赋值情况,将输入变量的所有取值组合和与之相对应的输出函数值列表,即得真值表。注意,不会出现或不允许出现的输入变量取值组合可以不列出,如果列出,可在相应的输出函数处记上“×”号,化简时可作约束项处理。

(3)化简

用卡诺图法或公式法进行化简,得到最简逻辑函数表达式。

(4)画逻辑图

根据简化后的逻辑表达式画出逻辑电路图。如果对采用的门电路类型有要求,可遁当变换表达式形式(如与非、或非、与或非表达式等),然后用对应的门电路构成逻辑图。

设计举例:

例8-2试设计一个3人投票表决器,即3人中有2人或3人表示同意,则表决通过;否则为不通过。

解:首先,进行逻辑抽象。关键:

①弄清楚哪些是输入变量,哪些是输出变量;

②弄清楚输入变量与输出变量间的因果关系;

. ③对输入、输出变量进行状态赋值。

A、B、C是否同意为输入信号,决议是否通过为输出信号。设输入A(或B、C)为1表示同意,为O表示不同意;输出y为1表示决议通过,为O表示决议不通过。

第一步:确定输入、输出变量。

设A,B,C分别代表三人表决的逻辑变量。y代表表决的结果。

第二步:定义逻辑状态的含义。

设A,B,C为1表示赞成;O表示反对(反之亦然)。

热门点击

热门点击

- 继电器驱动电路中的二极管保护电路

- 电子电路焊接基本知识

- 放大器组成及各元件的作用

- 稳压二极管种类和外形特征

- 负反馈放大器的四种基本类型

- 影响器件功耗的主要因素

- 石英晶体――门电路多谐振荡器

- LED电平指示器种类

- NTC热敏电阻器抑制浪涌电路

- 穿心电容电路

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607