设计参考电路

发布时间:2012/2/6 20:51:55 访问次数:2721

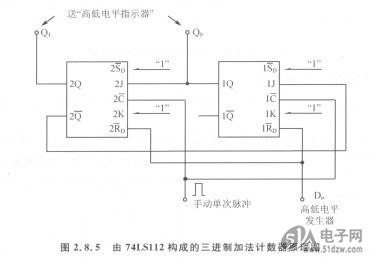

1.同步三进制加法计数器EET1102G

在这项实验中,利用74LS112的两个J-K触发器构成同步三进制加法计数器,其电路如图2.8.5所示。

该电路设计将两J-K触发器的复位端1RD和2RD接“高低电平”信号。当1RD一2RD一0时,计数器复位,io=20=o,当1RD一2RD一1时,计数器进入计数状态。

将K置高电平,J-K触发器工作在“记0”、“计数”两工作状态。电路工作时,首先将计数器清零复位,使1Q= 2Q=O。再送入时钟脉冲:当第一时钟脉冲到来时,因为1Q= 2Q=O,因而1J一2Q=1,2J一io=o,则触发器的状态1Q=1,2Q=0。在第二时钟脉冲到来时1J一2Q=1,2J一1Q=1都为“计数”状态,1Q翻转为0,2Q翻转为1。第三脉冲到来时,1J一2Q=O,2J =1Q-O,两触发器都为“记零”状态,这时1Q=2Q=O。这样就完成了三进制加法计数器一个完整的周期。

两个J-K触发器的置位端SD在电路中接往高电平。

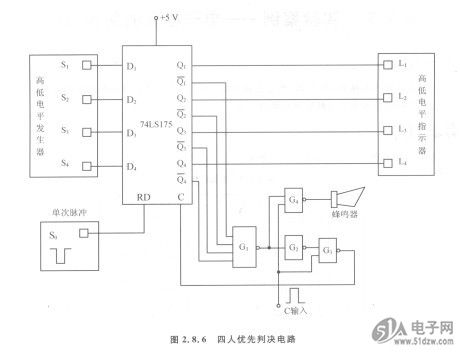

2.优先判决实验电路的工作原理

优先判决电踣俗称抢答器。它主要由输入开关、判决器、灯光显示电路及音响电路等部分组成。图2.8.6是由四D触发器74LS175等器件组成的四人抢答原理电路。输入开关和灯光显示我们借用数字学习机上的高低电平发生器和高低电平指示器。四D触发器74LS175,四输入与非门74LS20及2输入与非门74LSOO组成判别器。数字学习机上的1 kHz TTL矩形脉冲为判别器提供时钟,同时作为声音信号,经控制门G4,送蜂鸣器。

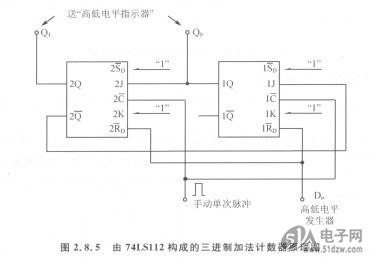

1.同步三进制加法计数器EET1102G

在这项实验中,利用74LS112的两个J-K触发器构成同步三进制加法计数器,其电路如图2.8.5所示。

该电路设计将两J-K触发器的复位端1RD和2RD接“高低电平”信号。当1RD一2RD一0时,计数器复位,io=20=o,当1RD一2RD一1时,计数器进入计数状态。

将K置高电平,J-K触发器工作在“记0”、“计数”两工作状态。电路工作时,首先将计数器清零复位,使1Q= 2Q=O。再送入时钟脉冲:当第一时钟脉冲到来时,因为1Q= 2Q=O,因而1J一2Q=1,2J一io=o,则触发器的状态1Q=1,2Q=0。在第二时钟脉冲到来时1J一2Q=1,2J一1Q=1都为“计数”状态,1Q翻转为0,2Q翻转为1。第三脉冲到来时,1J一2Q=O,2J =1Q-O,两触发器都为“记零”状态,这时1Q=2Q=O。这样就完成了三进制加法计数器一个完整的周期。

两个J-K触发器的置位端SD在电路中接往高电平。

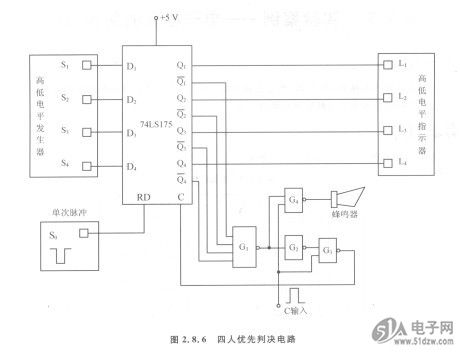

2.优先判决实验电路的工作原理

优先判决电踣俗称抢答器。它主要由输入开关、判决器、灯光显示电路及音响电路等部分组成。图2.8.6是由四D触发器74LS175等器件组成的四人抢答原理电路。输入开关和灯光显示我们借用数字学习机上的高低电平发生器和高低电平指示器。四D触发器74LS175,四输入与非门74LS20及2输入与非门74LSOO组成判别器。数字学习机上的1 kHz TTL矩形脉冲为判别器提供时钟,同时作为声音信号,经控制门G4,送蜂鸣器。

上一篇:四D触发器74LS175集成块

上一篇:电子秒表的原理

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607