锁相回路

发布时间:2011/12/22 9:59:35 访问次数:3894

而除了这个用途外,PLL还可以广泛使用在许多不同的通信应用中,例如电视机、音调译码器(tone decoder)、遥测接收器(telemetry receiver)、调制解调器及数据同步器等。这些应用中有许多会在通信电子课程里学习到。事实上,有完整专门的书籍深入介绍关于PLL的操作、分析及应用等。本节将重点放在PLL基本概念的介绍,我们将让你对PLL工作原理有直觉上的理解,也让你了解如何将PLL应用在FM解调制上。另外,我们会介绍一个特殊的PLL集成电路元件。

在学完本节后,我们应该能够:说明锁相回路( PLL)的基本概念;绘出PLL的基本框图;参与讨论相位检测器(phase detector)并说明其功能;说明VCO朐用途;解释低通滤波器的用途;解释锁定范围(lock range)及捕捉范围(capture range)的意义;参与讨论LM565 PLL的相关性质以及如何使用它组成FM解调制器。

1.PLL的基本观念

锁相回路(PLL)是由相位检测器(phase detector)、低通滤波器、电压控制振荡器(VCO)所组成的反馈电路。不过,有些PLL回路会包含放大器,而在另一些应用电路里,可能不需要使用滤波器。

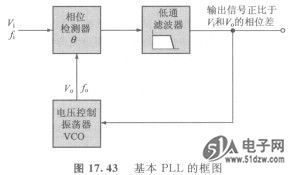

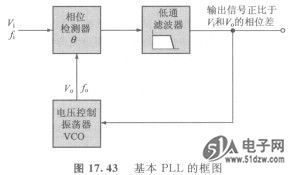

PLL能够锁定进入回路的信号相位,或是与进入回路的信号同步。当进入回路的信号相位改变时,代表频率发生变化,此时相位检测器的输出电压会适当的增加或是变小,使得VCO的频率与进入回路的信号相同。如图17.43所示为基本PLL的框图。

PLL的基本工作原理如下:相位检测器会比较进入回路的信号Vi与VC()输出信号Vo之间的相位差。当进入回路的信号频率^与VCO输出信号的频率fo不同时,两个信号之间的相位角也会不同。相位检测器与滤波器的输出电压会正比于两个信号间的相位差。这个按比例变动的电压会输入VCO,强迫VCO的输出频率移向输入信号频率,直到两者相等力止。此时PLL即锁定为进入回路的信号频率。如果fi改变,相位差也会跟着改变,这将强迫VCO追踪进入回路信号的频率。

2.相位检测器

PLL内的相位检测电路基本上是一个线性倍增器。下面的分析将说明它在PLL内部的工作原理。进入回路的信号Vi及VCO信号Vo送到相位检测器的输入端,这两个信号可以表示为

υi=Visin(2πfit+θi)

υo=Vosin(2πfot+θo)

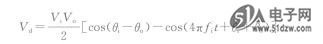

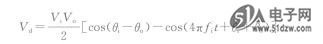

其中θ1和θ2分别为两个信号的相对相位角。相位检测器将两个信号相乘,并产生差频率以及和频率的输出信号Vd,过程如下:

当PLL锁定信号时, fi=fo

而且 2πfit=2πfot

所以,检测器的输出电压为

上式中的第二个余弦函数为fi的第二谐波(2×2πfit),会被低通滤波器滤除。由滤波器所输出的VCO控制

电压可以表示如下:

Vc=ViVo/2×cosθe (17.4)

其中θe=θi-θo,而θe即为相位误差(phase error)。因此滤波器的输出电压值会正比于进入回路信号与VCO输出信号之间的相位差,并且可以利用这个电压来控制VCO。整个过程如图17. 44所示。

3.电压控制振荡器

电压控制振荡器有很多种形式。无论是哪一种,大部分使用于PLL的VCO都是根据可变电抗(variable reactance)的工作原理,就是使用变容二极管作为电压控制可变电容器。

变容二极管的电容量与反向偏压的大小成反比。其电容值随着反向偏压的增大而减小,反之亦然。

在L中,反馈到VCO的控制电压形成VCO内变容二极管的反向偏压。根据下列公式可知,RC振荡器的振荡频率与电容值成反比: fo=1/2πRC

而振荡器的振荡频率则为 fo=1/2πLC

由上述公式可知,频率随着电容值的减小而增加,反之亦然。

当反向偏压(控制电压)增加时,电容值将减小。因此,增加VCO的控制电压会使频率增加,反之亦然。如图17. 45所示为基本VCO的工作情形。图17. 45(b)则显示在额定控制电压Uc(nom)下,振荡器将工作于额定或自发振荡频率( free-running frequency)fo(nom)。将Vc增加到超过额定值,会迫使振荡器频率增加;而将Vc减少到低于额定值,会迫使振荡器频率减小。当然,如图中所示整个运作过程受到最小值与最大值的限制。VCO的转换函数(transfer function)或者变换增益(conversion gain)K,通常是以控制电压的每单位改变量所对应的频率变化量来表示 K=△fo/△Vc

4.基本PLL工作原理

当PLL锁定时,进入回路的信号频率fi与VCO频率fo会相等。然而,它们之间永远存在一个相位差,称为静态相位误差(static phase error)。相位误差鼠是能够使PLL保持锁定的参数。我们已经知道,从相位检测器的输出电压正比于θe(式(17.4))。这个电压能控制VCO的频率,而且其值刚好可以让fo=f1。

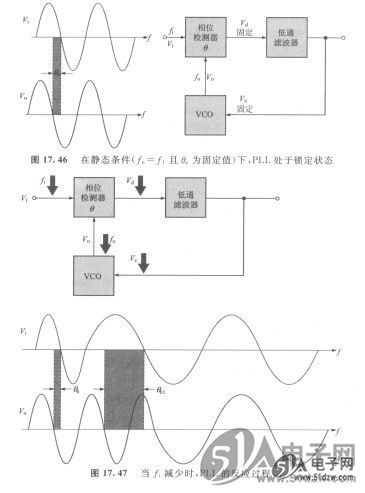

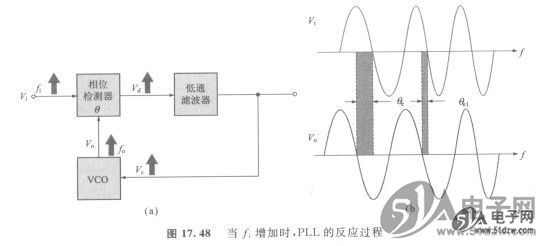

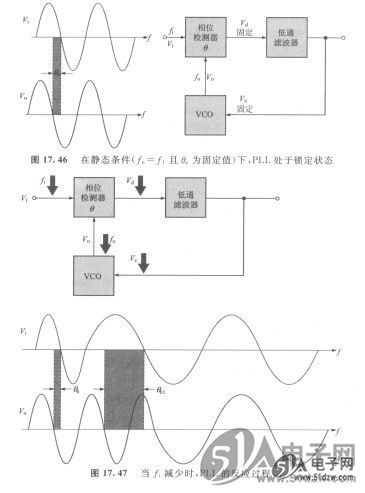

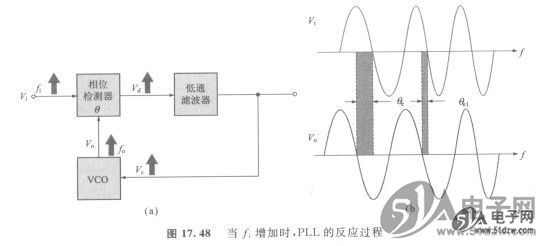

如图17. 46所示为PLL与两个频率相等但相位差为臼。的正弦波信号。在此条件下,PLL处于锁定状态,而且VCO控制电压是固定值。如图17.47所示,假设fi变小,θe会增加到θe1。θe的增加量被相位检测器感测到,使得VCO控制电压减少,因此fo开始减小直到fo= fi,然后使PLL保持在锁定状态。如图17.48所示,假设fi增加,则晚减少到θe1,θe的减小量会导致VCO控制电压增加,因此fo会开始变大直到fo=fi,然后使PLL保持在锁定状态。

(1)锁定范围

一旦PLL锁定,它会开始追踪输入信号的频率变化。PLL可以保持在锁定状态的频率范围称为锁定范围(lock range)或追踪范围。锁定范围的限制为VCO的最大频率偏移量,以及相位检测器的输出限制。锁定范围与低通滤波器的频宽无关,这是因为当PLL处于锁定状态时,差频率(fi-fo)为零或极小的瞬间值,因此会安全地落于此频宽范围内。锁定范围通常以VCO频率的某个百分比加以表示。

(2)捕捉范围

假设PLL不是处于锁定状态,PLL能够达到与输入信号锁定的频率范围称为捕捉范围(capture range)aPLL要达到锁定状态需要两个基本条件。第一,差频率(fi-fo)必须低到足够落在滤波器的频宽内。也就是说,进入回路的信号频率与VCO的额定或自发振荡频率的差距,必须不能超过低通滤波器的频宽。第二,VCO振荡频率的最大偏移量△fax,必须足以使得fo增加或减少到与工相等。这些条件的说明显示在图17,49中,MC33035PG当这些条件成立时,PLL会把VCO的频率向进入回路的信号频率“拉拢”,直到fo=fi.

而除了这个用途外,PLL还可以广泛使用在许多不同的通信应用中,例如电视机、音调译码器(tone decoder)、遥测接收器(telemetry receiver)、调制解调器及数据同步器等。这些应用中有许多会在通信电子课程里学习到。事实上,有完整专门的书籍深入介绍关于PLL的操作、分析及应用等。本节将重点放在PLL基本概念的介绍,我们将让你对PLL工作原理有直觉上的理解,也让你了解如何将PLL应用在FM解调制上。另外,我们会介绍一个特殊的PLL集成电路元件。

在学完本节后,我们应该能够:说明锁相回路( PLL)的基本概念;绘出PLL的基本框图;参与讨论相位检测器(phase detector)并说明其功能;说明VCO朐用途;解释低通滤波器的用途;解释锁定范围(lock range)及捕捉范围(capture range)的意义;参与讨论LM565 PLL的相关性质以及如何使用它组成FM解调制器。

1.PLL的基本观念

锁相回路(PLL)是由相位检测器(phase detector)、低通滤波器、电压控制振荡器(VCO)所组成的反馈电路。不过,有些PLL回路会包含放大器,而在另一些应用电路里,可能不需要使用滤波器。

PLL能够锁定进入回路的信号相位,或是与进入回路的信号同步。当进入回路的信号相位改变时,代表频率发生变化,此时相位检测器的输出电压会适当的增加或是变小,使得VCO的频率与进入回路的信号相同。如图17.43所示为基本PLL的框图。

PLL的基本工作原理如下:相位检测器会比较进入回路的信号Vi与VC()输出信号Vo之间的相位差。当进入回路的信号频率^与VCO输出信号的频率fo不同时,两个信号之间的相位角也会不同。相位检测器与滤波器的输出电压会正比于两个信号间的相位差。这个按比例变动的电压会输入VCO,强迫VCO的输出频率移向输入信号频率,直到两者相等力止。此时PLL即锁定为进入回路的信号频率。如果fi改变,相位差也会跟着改变,这将强迫VCO追踪进入回路信号的频率。

2.相位检测器

PLL内的相位检测电路基本上是一个线性倍增器。下面的分析将说明它在PLL内部的工作原理。进入回路的信号Vi及VCO信号Vo送到相位检测器的输入端,这两个信号可以表示为

υi=Visin(2πfit+θi)

υo=Vosin(2πfot+θo)

其中θ1和θ2分别为两个信号的相对相位角。相位检测器将两个信号相乘,并产生差频率以及和频率的输出信号Vd,过程如下:

当PLL锁定信号时, fi=fo

而且 2πfit=2πfot

所以,检测器的输出电压为

上式中的第二个余弦函数为fi的第二谐波(2×2πfit),会被低通滤波器滤除。由滤波器所输出的VCO控制

电压可以表示如下:

Vc=ViVo/2×cosθe (17.4)

其中θe=θi-θo,而θe即为相位误差(phase error)。因此滤波器的输出电压值会正比于进入回路信号与VCO输出信号之间的相位差,并且可以利用这个电压来控制VCO。整个过程如图17. 44所示。

3.电压控制振荡器

电压控制振荡器有很多种形式。无论是哪一种,大部分使用于PLL的VCO都是根据可变电抗(variable reactance)的工作原理,就是使用变容二极管作为电压控制可变电容器。

变容二极管的电容量与反向偏压的大小成反比。其电容值随着反向偏压的增大而减小,反之亦然。

在L中,反馈到VCO的控制电压形成VCO内变容二极管的反向偏压。根据下列公式可知,RC振荡器的振荡频率与电容值成反比: fo=1/2πRC

而振荡器的振荡频率则为 fo=1/2πLC

由上述公式可知,频率随着电容值的减小而增加,反之亦然。

当反向偏压(控制电压)增加时,电容值将减小。因此,增加VCO的控制电压会使频率增加,反之亦然。如图17. 45所示为基本VCO的工作情形。图17. 45(b)则显示在额定控制电压Uc(nom)下,振荡器将工作于额定或自发振荡频率( free-running frequency)fo(nom)。将Vc增加到超过额定值,会迫使振荡器频率增加;而将Vc减少到低于额定值,会迫使振荡器频率减小。当然,如图中所示整个运作过程受到最小值与最大值的限制。VCO的转换函数(transfer function)或者变换增益(conversion gain)K,通常是以控制电压的每单位改变量所对应的频率变化量来表示 K=△fo/△Vc

4.基本PLL工作原理

当PLL锁定时,进入回路的信号频率fi与VCO频率fo会相等。然而,它们之间永远存在一个相位差,称为静态相位误差(static phase error)。相位误差鼠是能够使PLL保持锁定的参数。我们已经知道,从相位检测器的输出电压正比于θe(式(17.4))。这个电压能控制VCO的频率,而且其值刚好可以让fo=f1。

如图17. 46所示为PLL与两个频率相等但相位差为臼。的正弦波信号。在此条件下,PLL处于锁定状态,而且VCO控制电压是固定值。如图17.47所示,假设fi变小,θe会增加到θe1。θe的增加量被相位检测器感测到,使得VCO控制电压减少,因此fo开始减小直到fo= fi,然后使PLL保持在锁定状态。如图17.48所示,假设fi增加,则晚减少到θe1,θe的减小量会导致VCO控制电压增加,因此fo会开始变大直到fo=fi,然后使PLL保持在锁定状态。

(1)锁定范围

一旦PLL锁定,它会开始追踪输入信号的频率变化。PLL可以保持在锁定状态的频率范围称为锁定范围(lock range)或追踪范围。锁定范围的限制为VCO的最大频率偏移量,以及相位检测器的输出限制。锁定范围与低通滤波器的频宽无关,这是因为当PLL处于锁定状态时,差频率(fi-fo)为零或极小的瞬间值,因此会安全地落于此频宽范围内。锁定范围通常以VCO频率的某个百分比加以表示。

(2)捕捉范围

假设PLL不是处于锁定状态,PLL能够达到与输入信号锁定的频率范围称为捕捉范围(capture range)aPLL要达到锁定状态需要两个基本条件。第一,差频率(fi-fo)必须低到足够落在滤波器的频宽内。也就是说,进入回路的信号频率与VCO的额定或自发振荡频率的差距,必须不能超过低通滤波器的频宽。第二,VCO振荡频率的最大偏移量△fax,必须足以使得fo增加或减少到与工相等。这些条件的说明显示在图17,49中,MC33035PG当这些条件成立时,PLL会把VCO的频率向进入回路的信号频率“拉拢”,直到fo=fi.

上一篇:频率调制

上一篇:当作FM解调制器的PLL

热门点击

热门点击

- NPN型三极管各电极电压与电流的关系

- 图解电阻分压电路结构

- 变容二极管它的结电容值会随着反向偏压而改变

- 集成运放反相器电路

- 闭路电视的安装

- 漏电保护器的接线

- N型与P型半导体

- 推挽式MOSFET放大器

- 电压跟随器

- 电阻器的作用

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607