绝缘介质在薄膜层之间均匀无孔填充提供充分有效隔离保护

发布时间:2023/10/3 13:27:04 访问次数:103

高乃介质的一个挑战是维持器件的高驱动电流,如前所述,在高乃介质上面采用金属电极取代多晶硅,可以减少沟道内电子迁移率损失,但还需要在高虑介质和⒏基底之间加入Si()2/Si()N作为界面缓冲层,进一步改善电子迁移率。

界面层还有助于界面的稳定性和器件的可靠性,因为在以前多个技术节点,⒏o2/Si()N与⒏基底界面的优化已经研究得十分深人了。当然,界面层的存在也有不利的一面,它使得整体栅极介质的乃值降低,从而影响Ef)T的降低,所以必须严格控制它的厚度。

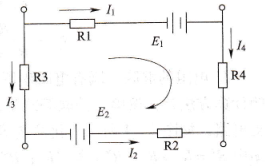

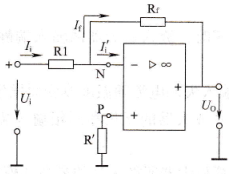

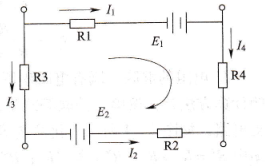

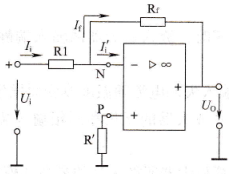

电子电路的连接关系,如果电路中多个负载首尾相连,那么就称它们的连接状态是串联的,为串联电路。

高密度等离子体化学气相沉积(HDP CVD)工艺被先进的芯片工厂采用以来,以其卓越的填孔能力、稳定的沉积质量、可靠的电学特性等诸多优点而迅速成为0.25um以下先进I艺的主流。

HfO2族的高乃介质是目前最好的替代SlO2/SlON的选择。

HfO2族的高乃介质是目前最好的替代SlO2/SlON的选择。

纯的Hf02具有较高的虍值(25),但缺点是无法承受高温。在温度超过500℃,Hf02会发生晶化,产生晶界缺陷,同时晶化还会造成表面粗糙度的增加,这都会引起漏电流的增加,从而影响器件的性能。

所以纯的HfO2只适合应用于后栅极后高虑的整合路线。

可以通过对Hfo2进行掺杂来改善它的高温性能,如掺Si或氮化,形成Hsi()/H⒗iON。但这样都会降低介质的乃值(15),从而影响EOT的降低。

深圳市慈安科技有限公司http://cakj.51dzw.com

高乃介质的一个挑战是维持器件的高驱动电流,如前所述,在高乃介质上面采用金属电极取代多晶硅,可以减少沟道内电子迁移率损失,但还需要在高虑介质和⒏基底之间加入Si()2/Si()N作为界面缓冲层,进一步改善电子迁移率。

界面层还有助于界面的稳定性和器件的可靠性,因为在以前多个技术节点,⒏o2/Si()N与⒏基底界面的优化已经研究得十分深人了。当然,界面层的存在也有不利的一面,它使得整体栅极介质的乃值降低,从而影响Ef)T的降低,所以必须严格控制它的厚度。

电子电路的连接关系,如果电路中多个负载首尾相连,那么就称它们的连接状态是串联的,为串联电路。

高密度等离子体化学气相沉积(HDP CVD)工艺被先进的芯片工厂采用以来,以其卓越的填孔能力、稳定的沉积质量、可靠的电学特性等诸多优点而迅速成为0.25um以下先进I艺的主流。

HfO2族的高乃介质是目前最好的替代SlO2/SlON的选择。

HfO2族的高乃介质是目前最好的替代SlO2/SlON的选择。

纯的Hf02具有较高的虍值(25),但缺点是无法承受高温。在温度超过500℃,Hf02会发生晶化,产生晶界缺陷,同时晶化还会造成表面粗糙度的增加,这都会引起漏电流的增加,从而影响器件的性能。

所以纯的HfO2只适合应用于后栅极后高虑的整合路线。

可以通过对Hfo2进行掺杂来改善它的高温性能,如掺Si或氮化,形成Hsi()/H⒗iON。但这样都会降低介质的乃值(15),从而影响EOT的降低。

深圳市慈安科技有限公司http://cakj.51dzw.com

公网安备44030402000607

公网安备44030402000607