内部射频模块的滤波电容陶瓷无引线芯片载体

发布时间:2020/12/27 21:57:54 访问次数:820

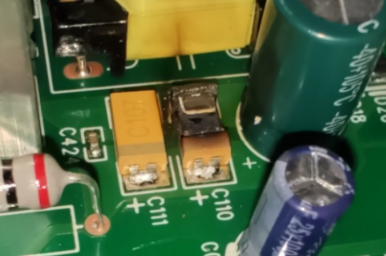

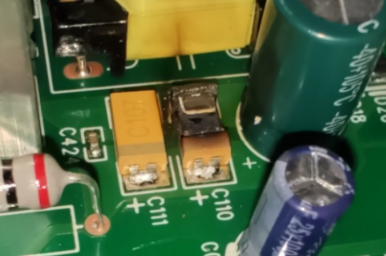

外围电源去耦电容 C4、C6 和 C9,可以滤除电源上的干扰信号。其中,特别需要注意的是 C6,建议最小取值 10uF,对于一些干扰很大的应用,建议增加到 22 μF 以上。C4和 C9一般取0.1 μF即可。需要注意的是 C5,是芯片内部数字模块的滤波电容,推荐焊接,可以增强数字电路的稳定性。C3 是内部射频模块的滤波电容,一般不用焊接。

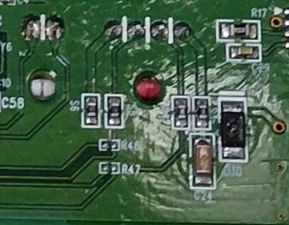

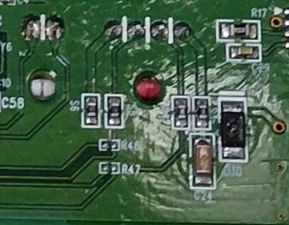

HW2181B 2.4 GHz无线通信系统对PCB(印制板)设计有比较高的要求,设计不好会影响通信距离。

射频 PCB 对于布局和布线都有一定的要求。

CMOS图像传感器采用了一种新型的业内标准--32针CLCC(陶瓷无引线芯片载体)封装形式。这种封装的规格为10.7 mmx10.7 mm x 1.65 mm;而以往安捷伦图像传感器所采用的PQFP(塑料四方扁平封装)封装的规格则是13.5 mmx14.5 mmx3.80 mm。

由于管脚是扁平的,所以CLCC封装的顶部是平直的,从而可以对高度实现更加精确的布局,进而更加迅速、简便地对光进行调节。新的封装还增强了热性能,可以在更广泛的温度范围内保证工作的稳定性。

这些CMOS图像传感器还为在各种光线条件下捕获更加详细的图像提供了高度灵敏的低噪声设计。

128Kx72全三元的IP协处理器。这是目前业内速度最快、搜寻范围最宽的处理器,其先进的管理特点可提高系统性能并降低能耗。IDT还计划于2002年9月推出256Kx72 IP协同处理器,从而完善这一系列。

亚洲的系统设计人员利用功率控制的特点,在实际应用环境下可降低能耗达60%。IDT通过提供HDL编码以支持基于FPGA和ASIC的编程,以及提供软件工具支持基于NPU的设计, 这些都能帮助设备厂商在使用这些器件时缩短产品上市时间。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

外围电源去耦电容 C4、C6 和 C9,可以滤除电源上的干扰信号。其中,特别需要注意的是 C6,建议最小取值 10uF,对于一些干扰很大的应用,建议增加到 22 μF 以上。C4和 C9一般取0.1 μF即可。需要注意的是 C5,是芯片内部数字模块的滤波电容,推荐焊接,可以增强数字电路的稳定性。C3 是内部射频模块的滤波电容,一般不用焊接。

HW2181B 2.4 GHz无线通信系统对PCB(印制板)设计有比较高的要求,设计不好会影响通信距离。

射频 PCB 对于布局和布线都有一定的要求。

CMOS图像传感器采用了一种新型的业内标准--32针CLCC(陶瓷无引线芯片载体)封装形式。这种封装的规格为10.7 mmx10.7 mm x 1.65 mm;而以往安捷伦图像传感器所采用的PQFP(塑料四方扁平封装)封装的规格则是13.5 mmx14.5 mmx3.80 mm。

由于管脚是扁平的,所以CLCC封装的顶部是平直的,从而可以对高度实现更加精确的布局,进而更加迅速、简便地对光进行调节。新的封装还增强了热性能,可以在更广泛的温度范围内保证工作的稳定性。

这些CMOS图像传感器还为在各种光线条件下捕获更加详细的图像提供了高度灵敏的低噪声设计。

128Kx72全三元的IP协处理器。这是目前业内速度最快、搜寻范围最宽的处理器,其先进的管理特点可提高系统性能并降低能耗。IDT还计划于2002年9月推出256Kx72 IP协同处理器,从而完善这一系列。

亚洲的系统设计人员利用功率控制的特点,在实际应用环境下可降低能耗达60%。IDT通过提供HDL编码以支持基于FPGA和ASIC的编程,以及提供软件工具支持基于NPU的设计, 这些都能帮助设备厂商在使用这些器件时缩短产品上市时间。

(素材来源:eccn和ttic.如涉版权请联系删除。特别感谢)

公网安备44030402000607

公网安备44030402000607