CMOS微控制器和发射器电路

发布时间:2020/8/19 0:25:03 访问次数:1117

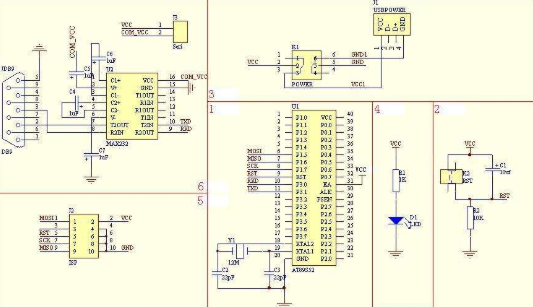

rfPIC12C509AF内部结构包括一个完整的8位CMOS微控制器电路和发射器电路,以下介绍发射器电路。发射器电路方框图。

发射器是一个完整的集成UHF ASK/FSK发射电路,由石英晶体振荡器、锁相环电路(PLL)、集电极开路的输出功率可变放大器PA(Power Amplifier)和模式控制逻辑(mode control logic)所组成。外接元件有旁路电容、晶振和PLL回路滤波器,能实现ASK和FSK的操作。

引脚VDDRF和VSSRF分别是发射器电路的电源供给端和接地端。这些电源脚与微控制器的电源供给脚VDD和VSS是相互独立的.

C1取值22~1000pF,C2取值47~1000pF。

发射器中心频率(fc):fc=(fMAX+fMIN)/2

发射器频率偏差:Δf=(fMAX-fMIN)/2

石英晶体振荡器有1个四分频(Divide by 4)电路,此电路通过时钟输出(CLKOUT)引脚输出时钟。CLKOUT时钟输出信号可作为微控制器的输入或其它外围电路的稳定基准频率。注意千万不要将CLKOUT信号连接到PIC微控制器的OSC1输入端,因为PIC微控制器没有时钟信号就不能工作,此时发射器的振荡器也不能工作。这时PIC微控制器需要从外部引入时钟或经过内部RC振荡器产生时钟。当应用中需要稳定的基准频率时,可将CLKOUT脚连接到GP2/T0CKI输入上,并且使用TIMER0模块。为了使干扰信号习尽可能小,应对CLKOUT有速率限制。CLKOUT的电压幅值由在CLKOUT脚上的充电电容决定(2VPP,5pF)。

锁相环电路(PLL)由相频检波器(phase frequency detector)、充电泵(charge pump)、压控振荡器VCO(Voltage Controlled Oscillator)和固定的32分频器(fixed divide by 32)组成。引脚LF连接1个外部回路滤波器。这个回路滤波器控制PLL的动态范围和起始锁定时间。

PLL的输出给功率入大器(PA)。集电极开路输出的不同值可直接驱动闭环天线(ANT1、ANT2)或经过1个阻抗匹配网络或平衡-不平衡变换器改变成单端口输出。引脚ANT1和ANT2为集电极开路输出,必须通过负载上拉到VDDRF。

PA的差动输出应该匹配1个1kΩ的负载电阻。当匹配不合理时会导致过度的干扰和谐波辐射。发射输出功率可以通过改变PS/DATAASK脚的电压调节成+2~-12dBm中的6个等分值。

在FSK的操作中,PS/DATAASK脚只能作为功率选择脚(PS)使用。1个20μA的内部电流源输出电流流入PS/DATAASK脚,通过电阻R2产生一个电压降,作为功率控制电压(VPS)控制发射输出功率。VPS控制PA的偏置电流,高的发射功率需要较大的偏置电流。

为了实现ASK操作,PA/DATAASK脚的功能是控制功率放大器PA导通或关断。分压网络上的R1和R2是为了确定VPS,以达到选择发射器输出功率的目的。假如要得到最大发射器输出功率,可以把引脚GP0和PA/DATAASK直接连接起来。

逻辑控制模引式脚RFENIN控制着发射器的操作。当RFENIN=1时,发射器和CLKOUT在工作模式;当RFENIN=0时,发射器和CLKOUT进入待机模式。在待机模式时,发射机产生很小的电流。REFNIN脚在内部有1个下拉电阻。

(素材来源:eccn和21ic.如涉版权请联系删除。特别感谢)

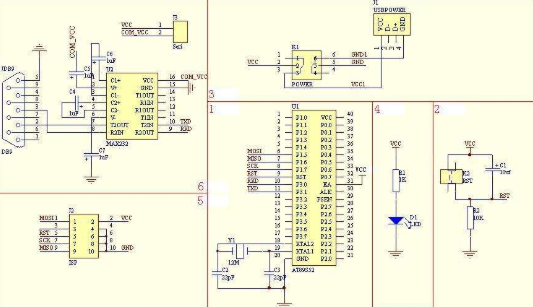

(素材来源:eccn和21ic.如涉版权请联系删除。特别感谢) rfPIC12C509AF内部结构包括一个完整的8位CMOS微控制器电路和发射器电路,以下介绍发射器电路。发射器电路方框图。

发射器是一个完整的集成UHF ASK/FSK发射电路,由石英晶体振荡器、锁相环电路(PLL)、集电极开路的输出功率可变放大器PA(Power Amplifier)和模式控制逻辑(mode control logic)所组成。外接元件有旁路电容、晶振和PLL回路滤波器,能实现ASK和FSK的操作。

引脚VDDRF和VSSRF分别是发射器电路的电源供给端和接地端。这些电源脚与微控制器的电源供给脚VDD和VSS是相互独立的.

C1取值22~1000pF,C2取值47~1000pF。

发射器中心频率(fc):fc=(fMAX+fMIN)/2

发射器频率偏差:Δf=(fMAX-fMIN)/2

石英晶体振荡器有1个四分频(Divide by 4)电路,此电路通过时钟输出(CLKOUT)引脚输出时钟。CLKOUT时钟输出信号可作为微控制器的输入或其它外围电路的稳定基准频率。注意千万不要将CLKOUT信号连接到PIC微控制器的OSC1输入端,因为PIC微控制器没有时钟信号就不能工作,此时发射器的振荡器也不能工作。这时PIC微控制器需要从外部引入时钟或经过内部RC振荡器产生时钟。当应用中需要稳定的基准频率时,可将CLKOUT脚连接到GP2/T0CKI输入上,并且使用TIMER0模块。为了使干扰信号习尽可能小,应对CLKOUT有速率限制。CLKOUT的电压幅值由在CLKOUT脚上的充电电容决定(2VPP,5pF)。

锁相环电路(PLL)由相频检波器(phase frequency detector)、充电泵(charge pump)、压控振荡器VCO(Voltage Controlled Oscillator)和固定的32分频器(fixed divide by 32)组成。引脚LF连接1个外部回路滤波器。这个回路滤波器控制PLL的动态范围和起始锁定时间。

PLL的输出给功率入大器(PA)。集电极开路输出的不同值可直接驱动闭环天线(ANT1、ANT2)或经过1个阻抗匹配网络或平衡-不平衡变换器改变成单端口输出。引脚ANT1和ANT2为集电极开路输出,必须通过负载上拉到VDDRF。

PA的差动输出应该匹配1个1kΩ的负载电阻。当匹配不合理时会导致过度的干扰和谐波辐射。发射输出功率可以通过改变PS/DATAASK脚的电压调节成+2~-12dBm中的6个等分值。

在FSK的操作中,PS/DATAASK脚只能作为功率选择脚(PS)使用。1个20μA的内部电流源输出电流流入PS/DATAASK脚,通过电阻R2产生一个电压降,作为功率控制电压(VPS)控制发射输出功率。VPS控制PA的偏置电流,高的发射功率需要较大的偏置电流。

为了实现ASK操作,PA/DATAASK脚的功能是控制功率放大器PA导通或关断。分压网络上的R1和R2是为了确定VPS,以达到选择发射器输出功率的目的。假如要得到最大发射器输出功率,可以把引脚GP0和PA/DATAASK直接连接起来。

逻辑控制模引式脚RFENIN控制着发射器的操作。当RFENIN=1时,发射器和CLKOUT在工作模式;当RFENIN=0时,发射器和CLKOUT进入待机模式。在待机模式时,发射机产生很小的电流。REFNIN脚在内部有1个下拉电阻。

(素材来源:eccn和21ic.如涉版权请联系删除。特别感谢)

(素材来源:eccn和21ic.如涉版权请联系删除。特别感谢) 上一篇:高压氮化镓功率晶体管固态断路器

公网安备44030402000607

公网安备44030402000607