HRPG-ASCA53C进制集成计数器

发布时间:2019/10/19 8:57:41 访问次数:1080

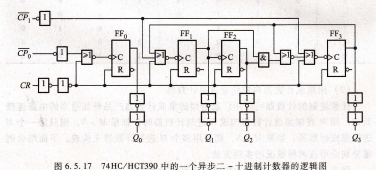

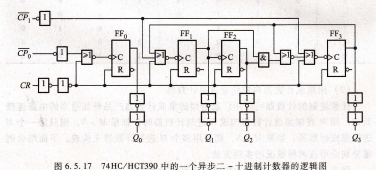

HRPG-ASCA53C图6.5.17 74HC/HCT390中的一个异步二一十进制计数器的逻辑图在例6.4.2中曾分析过一个异步五进制加计数电路,如果在其基础上增加一级触发器,便可构成异步二一十进制计数器。74HC/HCT390中集成的两个相同的二一十进制计数器便是基于这样的结构,图6.5.17所示是其中一个计数器的逻辑图。为了应用的灵活性,除清零信号C尺外,二进制计数器和五进制计数器的输人端、输出端均是独立引出的。

例6.5.2 将图6.5.17所示的电路按以下两种方式连接:

CPO接计数脉冲信号,将O0与CP1相连。

CP1接计数脉冲信号,将o3与CPO相连。

试分析它们的逻辑输出状态。

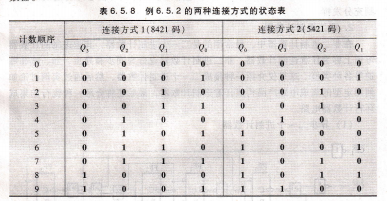

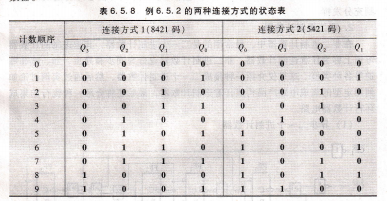

解:按①方式连接时,计数脉冲先进行二分频,然后进行五分频。从0000状态开始,依次分析,得到的状态表如表6,5.8左半边所示。Q3、Q2、Ol、O0输出为8421 BCD码。

按②方式连接时,计数脉冲先进行五分频,然后再二分频。分析得到的状态表列于表6.5.8右半边。可以看出,Q。的权值等于5,03、02、01的权值分别为4、2、1,这种编码称为5421 BCD码。因此,电路构成5421 BCD码计数器。

进制集成计数器;如果″<Ⅳ,则要用多个M进制计数器来构成。下面结合例题分别介绍这两种情况的实现方法。

例6.5.3 用74LⅤC161构成九进制加计数器。

解:九进制计数器应有9个状态,而74LVC161在计数过程中有16个状态。因此属于乃r)Ⅳ的情况。如果设法跳过多余的7个状态,则可实现模9计数器。通常用两种方法实现,即反馈清零法和反馈置数法。

HRPG-ASCA53C图6.5.17 74HC/HCT390中的一个异步二一十进制计数器的逻辑图在例6.4.2中曾分析过一个异步五进制加计数电路,如果在其基础上增加一级触发器,便可构成异步二一十进制计数器。74HC/HCT390中集成的两个相同的二一十进制计数器便是基于这样的结构,图6.5.17所示是其中一个计数器的逻辑图。为了应用的灵活性,除清零信号C尺外,二进制计数器和五进制计数器的输人端、输出端均是独立引出的。

例6.5.2 将图6.5.17所示的电路按以下两种方式连接:

CPO接计数脉冲信号,将O0与CP1相连。

CP1接计数脉冲信号,将o3与CPO相连。

试分析它们的逻辑输出状态。

解:按①方式连接时,计数脉冲先进行二分频,然后进行五分频。从0000状态开始,依次分析,得到的状态表如表6,5.8左半边所示。Q3、Q2、Ol、O0输出为8421 BCD码。

按②方式连接时,计数脉冲先进行五分频,然后再二分频。分析得到的状态表列于表6.5.8右半边。可以看出,Q。的权值等于5,03、02、01的权值分别为4、2、1,这种编码称为5421 BCD码。因此,电路构成5421 BCD码计数器。

进制集成计数器;如果″<Ⅳ,则要用多个M进制计数器来构成。下面结合例题分别介绍这两种情况的实现方法。

例6.5.3 用74LⅤC161构成九进制加计数器。

解:九进制计数器应有9个状态,而74LVC161在计数过程中有16个状态。因此属于乃r)Ⅳ的情况。如果设法跳过多余的7个状态,则可实现模9计数器。通常用两种方法实现,即反馈清零法和反馈置数法。

公网安备44030402000607

公网安备44030402000607