HN58X2416TI24C16芯片的计数控制

发布时间:2019/10/18 23:54:17 访问次数:983

HN58X2416TI24C16时钟脉冲CP 是计数脉冲输人端,也是芯片内4个触发器的公共时钟输人端。

异步清零CR 当它为低电平时,无论其他输入端是何状态(包括时钟信号cP),都使片内所有触发器状态置0,称为异步清零。CR有优先级最高的控制权。下述各输人信号都是在CR=1时才起作用。

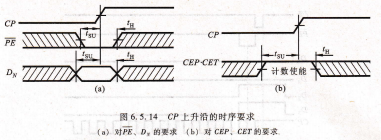

并行置数使能PE置数控制端。只需在CP上升沿之前保持低电平,数据输入端D3~DO的逻辑值便能在CP上升沿到来后置人片内4个相应触发器中。由于该操作与CP上升沿同步,且D3~DO的数据同时置入计数器,所以称为同步并行预置。为保证数据正确置入,要求PE在CP上升沿之前建立稳定的低电平,其最短提前时间称为建立时间莎sv,它们时序关系如图6,5.14(a)。PE置数操作具有次高优先级,仅低于CR,计数和保持操作时都要求PE=1。

数据输入端DⅣ(D3~DO) 在CP上升沿到来前至少提前砂st将预置数据摆在D3~D。输入端,且PE=0,则CP上升沿到来后,D3~DO便置人触发器。该时序与5.3.4节中所述D触发器相似。CP上升沿对DⅣ的时序要求亦如图6.5.14(a)所示。

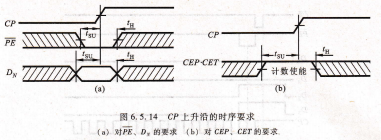

计数使能CEP 只要在CP上升沿到来前至少一个建立时间艺sr期间内保持高电平,且CEr=1,cP上升沿就能使计数器进行一次计数操作。它与CP上升沿的时序关系如图6.5.14(b)所示。CEP主要控制本芯片的计数操作。

计数使能CEr 该信号和CEP做与运算后实现对本芯片的计数控制,当CEr・cEP=o,即两个计数使能端中有0时,不管有无CP脉冲作用,计数器都将停止计数,保持原有状态;当CR=PE=CEP=CET=1时处于计数状态,其状态转换与表6.5.5相同。与CEP不同的是,CEr还直接控制着进位输出信号rC,CEP和CFr的典型接法和作用将在例6.5.1中说明。

计数输出QⅣ(O3~O。) 计数器中4个触发器的Q端状态输出。

进位信号rC 只有当CEr=1且0302Q1O0=1111时,rC才为1,表明下一个CP上升沿到来时将会有进位发生。

综合上述功能可以得到74LⅤC161的典型时序图,如图6,5,15所示。图中,当清零信号CR=0时,各触发器置0:当CR=1时,若PE=0,在下一个时钟脉冲上升沿到来后,各触发器的输出状态与预置的输人数据相同。在CR=PE1的条仵下,若cEP±CEr图6.5.15中从预置的1100开始计数,直到CEP・此后处于禁止计数的保持状态:αQ2ol0。=0010。进位信号rC只有在=1111出为1,其余时间均为0。

HN58X2416TI24C16时钟脉冲CP 是计数脉冲输人端,也是芯片内4个触发器的公共时钟输人端。

异步清零CR 当它为低电平时,无论其他输入端是何状态(包括时钟信号cP),都使片内所有触发器状态置0,称为异步清零。CR有优先级最高的控制权。下述各输人信号都是在CR=1时才起作用。

并行置数使能PE置数控制端。只需在CP上升沿之前保持低电平,数据输入端D3~DO的逻辑值便能在CP上升沿到来后置人片内4个相应触发器中。由于该操作与CP上升沿同步,且D3~DO的数据同时置入计数器,所以称为同步并行预置。为保证数据正确置入,要求PE在CP上升沿之前建立稳定的低电平,其最短提前时间称为建立时间莎sv,它们时序关系如图6,5.14(a)。PE置数操作具有次高优先级,仅低于CR,计数和保持操作时都要求PE=1。

数据输入端DⅣ(D3~DO) 在CP上升沿到来前至少提前砂st将预置数据摆在D3~D。输入端,且PE=0,则CP上升沿到来后,D3~DO便置人触发器。该时序与5.3.4节中所述D触发器相似。CP上升沿对DⅣ的时序要求亦如图6.5.14(a)所示。

计数使能CEP 只要在CP上升沿到来前至少一个建立时间艺sr期间内保持高电平,且CEr=1,cP上升沿就能使计数器进行一次计数操作。它与CP上升沿的时序关系如图6.5.14(b)所示。CEP主要控制本芯片的计数操作。

计数使能CEr 该信号和CEP做与运算后实现对本芯片的计数控制,当CEr・cEP=o,即两个计数使能端中有0时,不管有无CP脉冲作用,计数器都将停止计数,保持原有状态;当CR=PE=CEP=CET=1时处于计数状态,其状态转换与表6.5.5相同。与CEP不同的是,CEr还直接控制着进位输出信号rC,CEP和CFr的典型接法和作用将在例6.5.1中说明。

计数输出QⅣ(O3~O。) 计数器中4个触发器的Q端状态输出。

进位信号rC 只有当CEr=1且0302Q1O0=1111时,rC才为1,表明下一个CP上升沿到来时将会有进位发生。

综合上述功能可以得到74LⅤC161的典型时序图,如图6,5,15所示。图中,当清零信号CR=0时,各触发器置0:当CR=1时,若PE=0,在下一个时钟脉冲上升沿到来后,各触发器的输出状态与预置的输人数据相同。在CR=PE1的条仵下,若cEP±CEr图6.5.15中从预置的1100开始计数,直到CEP・此后处于禁止计数的保持状态:αQ2ol0。=0010。进位信号rC只有在=1111出为1,其余时间均为0。

热门点击

热门点击

- 电压一时间型分段器X、y时限的整定原则

- LA5112N 复杂的数字系统制作

- 馈线自动化的功能与类型

- 7次谐波的实用判据

- MAX6805US44D3+T CMOS集成

- 稳态实验主要是从有无整流负载

- LM4852LQ MOS管的开关特性

- 对半分割检索算法

- LM116H/883C CMOS门电路是否过

- TW9919 集成电路编码器

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607