SN74AUC245RGYR ENΪоƬ��ʹ���ź�

����ʱ��:2019/10/14 13:23:50 ���ʴ���:1683

SN74AUC245RGYRten1p

-1 bitAdder t12(A[2],B[2],tcmp[2],Suln[2],temp[3]);

-1 bltAdder u3(A[3],B[3],temp[3],Sum[3],temp[4]);

Cout=temp[4];

cnd

endrnoduic

module l bitAdder(A,B,Ci,Sum,Co);

input A,B,Ci;

output sum,Co;

assign sum=A^B^Ci;

endmodule

ͼ4.4.4(a)��ʾ�Ǵ���ʹ�ܿ��ƶ˵�8��-3�����ȱ����õ�·����Ϊ��������

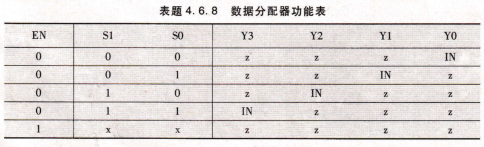

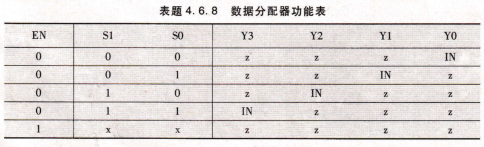

1·-4·���ݷ�������·�Ĺ��ܱ������4.6.8��ʾ,INΪ1·���������źţ�S1

S0Ϊѡ���ź�,ENΪоƬ��ʹ���ź�,Y3~Y0Ϊ����źš�xΪ����ֵ,zΪ����̬��Ҫ��:

��������Ƹõ�·,д����ƹ���,������ͼ��

��verihlog HDL����Ϊ��ģ��ʽ�����õ�·��

���������ϵͳ��,������Ҫ������������������㹦�ܵ��������·��,����Ҫ���д洢���ܵĵ�·,��ϵ�·��洢��·���Ͽɹ���ʱ������·,���ʱ���·�����½�����ʵ�ִ洢���ܵ���������Ԫ��·,���������ʹ������١������������ǵĵ�·�ṹ�빤��ԭ��,�Լ���ʵ�ֵIJ�ͬ�����ܡ�����,���»���������verilog HDL�����������봥�����ķ�����

�������ʹ������ֱ�ϵlatch��nip-flop����ơ�

SN74AUC245RGYRten1p

-1 bitAdder t12(A[2],B[2],tcmp[2],Suln[2],temp[3]);

-1 bltAdder u3(A[3],B[3],temp[3],Sum[3],temp[4]);

Cout=temp[4];

cnd

endrnoduic

module l bitAdder(A,B,Ci,Sum,Co);

input A,B,Ci;

output sum,Co;

assign sum=A^B^Ci;

endmodule

ͼ4.4.4(a)��ʾ�Ǵ���ʹ�ܿ��ƶ˵�8��-3�����ȱ����õ�·����Ϊ��������

1·-4·���ݷ�������·�Ĺ��ܱ������4.6.8��ʾ,INΪ1·���������źţ�S1

S0Ϊѡ���ź�,ENΪоƬ��ʹ���ź�,Y3~Y0Ϊ����źš�xΪ����ֵ,zΪ����̬��Ҫ��:

��������Ƹõ�·,д����ƹ���,������ͼ��

��verihlog HDL����Ϊ��ģ��ʽ�����õ�·��

���������ϵͳ��,������Ҫ������������������㹦�ܵ��������·��,����Ҫ���д洢���ܵĵ�·,��ϵ�·��洢��·���Ͽɹ���ʱ������·,���ʱ���·�����½�����ʵ�ִ洢���ܵ���������Ԫ��·,���������ʹ������١������������ǵĵ�·�ṹ�빤��ԭ��,�Լ���ʵ�ֵIJ�ͬ�����ܡ�����,���»���������verilog HDL�����������봥�����ķ�����

�������ʹ������ֱ�ϵlatch��nip-flop����ơ�

��������44030402000607

��������44030402000607