ICS1531Y-140 达林顿晶体管阵列

发布时间:2019/10/12 17:54:23 访问次数:1317

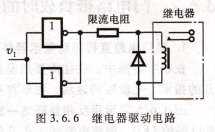

ICS1531Y-140如果负载所需的电流不特别大,例如微型继电器,可以将两个反相器并联作为驱动电路,如图3.6.6所示。即使封装在同一芯片内的两个反相器的参数也有差别,因此,并联后总的最大负载电流略小于单个门最大负载电流的两倍。

如果负载所需的电流比较大,达到几百毫安,则需要在数字电路的输出端与负 图3.6.6继电器驱动电路载之间接入一个功率驱动器件,称之为外围驱动器件。它的输入与数字集成电路(例如CMOS、TTL和ECL等)兼容,输出端可直接用于驱动机电系统。

外围驱动器件(例如达林顿晶体管阵列ULN2003 A等)的电路形式与结构一般都具有以下两个特点:一是采用集电极开路输出结构,其输出高电平凡乎等于外加电压,通过调节外加电压来满足不同负载对高电平电压的要求。二是驱动器电路的输出晶体管具有较强的带负载能力,能提供较大的电流。具体外围驱动器的电路结构可查阅有关数据手册。

抗干扰措施,利用逻辑门电路(CMOs或TTL)做具体的电路设计时,还应当注意下列几个实际问题:

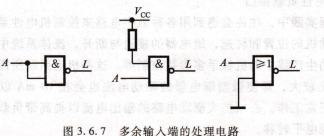

多余输入端的处理措施,集成逻辑门电路在使用时,一般不让多余的输入端悬空,以防止干扰信号引人。对多余输入端的处理以不改变电路工作状态及稳定可靠为原则,如图3,6.7所示。一是将它与其他输入端并接在一起。二是根据逻辑要求,与门或者与非门的多余输入端通过1~3 kΩ电阻接正电源,对CMOs电路可以直接接电源。或门或者或非门的多余输入端接地。对于高速电路的设计,并接会增加输入端等效电容性负载,而使信号的传输速度下降,最好采用图3.6.7所示的后两种方法。

ICS1531Y-140如果负载所需的电流不特别大,例如微型继电器,可以将两个反相器并联作为驱动电路,如图3.6.6所示。即使封装在同一芯片内的两个反相器的参数也有差别,因此,并联后总的最大负载电流略小于单个门最大负载电流的两倍。

如果负载所需的电流比较大,达到几百毫安,则需要在数字电路的输出端与负 图3.6.6继电器驱动电路载之间接入一个功率驱动器件,称之为外围驱动器件。它的输入与数字集成电路(例如CMOS、TTL和ECL等)兼容,输出端可直接用于驱动机电系统。

外围驱动器件(例如达林顿晶体管阵列ULN2003 A等)的电路形式与结构一般都具有以下两个特点:一是采用集电极开路输出结构,其输出高电平凡乎等于外加电压,通过调节外加电压来满足不同负载对高电平电压的要求。二是驱动器电路的输出晶体管具有较强的带负载能力,能提供较大的电流。具体外围驱动器的电路结构可查阅有关数据手册。

抗干扰措施,利用逻辑门电路(CMOs或TTL)做具体的电路设计时,还应当注意下列几个实际问题:

多余输入端的处理措施,集成逻辑门电路在使用时,一般不让多余的输入端悬空,以防止干扰信号引人。对多余输入端的处理以不改变电路工作状态及稳定可靠为原则,如图3,6.7所示。一是将它与其他输入端并接在一起。二是根据逻辑要求,与门或者与非门的多余输入端通过1~3 kΩ电阻接正电源,对CMOs电路可以直接接电源。或门或者或非门的多余输入端接地。对于高速电路的设计,并接会增加输入端等效电容性负载,而使信号的传输速度下降,最好采用图3.6.7所示的后两种方法。

上一篇:IX1877AF 机电性负载接口

公网安备44030402000607

公网安备44030402000607