Cadence/OrCAD PSpice 16.6流程

发布时间:2015/8/23 17:48:33 访问次数:1168

16.6以及16.6 QIR均对解决不收敛问题添加了很多的任选项,如图4.1.18所示,加框的表示16.6 QIR增加的选项。HD641719FL77由于一般的使用者很少去修改这些参数,所以对于具体的细节这里不再赘述。

Cadence/OrCAD PSpice 16.6流程

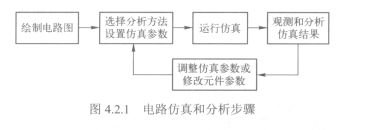

基于Cadence OrCAD的电路仿真和分析步骤如图4.2.1所示。首先根据设计电路在Capture原理图编辑环境下画出电路图,然后设置仿真参数,确定分析方法,执行PSpice仿真程序,最后在PSpice软件下观察、分析仿真运行结果,如果满足设计要求就可以结束仿真,如果还未满足要求,或者还没有全部分析出设计指标,可以修改元件参数或调整仿真参数重新选择分析方法运行仿真。

16.6以及16.6 QIR均对解决不收敛问题添加了很多的任选项,如图4.1.18所示,加框的表示16.6 QIR增加的选项。HD641719FL77由于一般的使用者很少去修改这些参数,所以对于具体的细节这里不再赘述。

Cadence/OrCAD PSpice 16.6流程

基于Cadence OrCAD的电路仿真和分析步骤如图4.2.1所示。首先根据设计电路在Capture原理图编辑环境下画出电路图,然后设置仿真参数,确定分析方法,执行PSpice仿真程序,最后在PSpice软件下观察、分析仿真运行结果,如果满足设计要求就可以结束仿真,如果还未满足要求,或者还没有全部分析出设计指标,可以修改元件参数或调整仿真参数重新选择分析方法运行仿真。

热门点击

热门点击

- 用异或门74LS86和与非门74LSOO设计

- 热敏电阻器的规格型号及主要参数

- 电位器的型号和主要参数

- 74LS163构成模6计数器

- 电感线圈的绕法

- 差分放大器的共模电压增益

- 晶闸管的工作特性及其特点

- 用万用表对蜂鸣器进行检测

- 用数据选择器实现组合逻辑函数

- 研究电压串联负反馈对输入、输出电阻的影响

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607