Cadence新一代Palladium Z2和Protium X2系统

发布时间:2021/4/8 8:33:54 访问次数:2594

关键词:arm v9架构 人工智能

楷登电子发布cadence palladium z2 enterprise emulation企业级硬件仿真加速系统和protium x2enterprise prototyping企业级原型验证系统,用于应对呈指数级上升的系统设计复杂度和上市时间的压力。

基于cadence原有的pallaidum z1和protiumx1产品,新一代系统为当前数十亿门规模的片上系统(soc)设计提供最佳的硅前硬件纠错效率和最高的软件调试吞吐率。

此双系统无缝集成统一的编译器和外设接口,双剑合璧,被称为系统动力双剑(dynamic duo)。

新一代系统基于下一代硬件仿真核心处理器和xilinx ultrascale+ vu19p fpga,将为客户带来2倍容量提升和1.5倍性能提升,以更少的时间为大规模芯片验证完成更多次数的迭代。

模块化编译技术也突破性地应用在两个系统中,使得100亿门的soc编译可以在palladium z2 系统10小时内即可完成,protium x2系统也仅需不到24小时就可以完成。

“我们对高端图形和超大规模设计的每一次升级都意味着复杂性的增加,上市时间也愈发紧张。”

nvidia公司硬件工程高级总监narendrakonda表示,

“采用结合cadence palladium z2和protium x2系统的通用前端流程,我们可以优化功能验证(verification)、功能确认(validation)和硅前软件初启的工作负载分布。得益于增加2倍的可用容量、提升50%的吞吐率以及更快的模块化编译循环,我们可以按时完成对最复杂gpu和soc设计的全面验证。”

palladium z2/protium x2 dynamic duo动力双剑组合被用于应对移动、消费电子和超大规模计算领域最先进应用设计所面临的挑战。

基于无缝集成的流程、统一的纠错、通用的虚拟和物理接口以及跨系统的测试平台内容,该动力双剑组合可以实现从硬件仿真到原型验证的快速设计迁移和测试。

“amd成功的重要成果之一,就是加速芯片开发流程并优化amd的左移战略。”

amd公司全球院士、方法学架构师alexstar说到,“采用cadence palladium z2 和 protium x2系统提升性能,在保证硬件仿真和原型验证间功能性一致的基础上,可以提升硅前工作负载的吞吐量。快速初启的能力以及在palladium z2硬件仿真与protiumx2原型验证间短时间切换能力,在开发最具挑战的soc设计时,为我们提供了优化自身的左移策略的机会。通过使用拥有业界领先的第三代amd epyc?处理器以及palladium z2和protium x2平台的资格认证的服务器,客户将能够将行业领先的性能计算带入palladium和protium生态系统。”

“先进soc设计的硅前验证需要具备数十亿门处理能力的解决方案,该方案须同时提供最高的性能以及快速可预测的纠错能力。”

cadence公司资深副总裁兼系统与验证事业部总经理paulcunningham表示,

“我们全新的dynamic duo动力双剑组合通过两个紧密集成的系统满足上述要求,包括针对快速可预测的硬件纠错优化的palladium z2硬件仿真加速系统,以及面向高性能数十亿门软件验证优化的protium x2原型验证系统。客户表达的强烈需求让我们深受鼓舞。cadence将继续与客户合作,利用新系统实现最高的设计验证吞吐率。”

“业界最佳的硬件仿真器是我们取得成功的关键,arm在基于arm的服务器上一直在广泛使用硬件仿真加速器和仿真工具,以实现最高的整体验证吞吐率。”

arm公司设计服务资深总监trannguyen表示,

“采用全新的cadencepalladiumz2系统,我们已经在最新设计上实现了超过50%的性能提升和2倍的容量增加,为我们提供了验证下一代ip和产品所需的强大的硅前验证能力。”

“xilinx与cadence紧密合作,确保cadence的软件前端能与后端的赛灵思vivado design suite设计套件无缝协作。”

xilinx公司关键应用市场资深总监hanneke krekels表示, “基于fpga的cadenceprotiumx2 原型验证平台让使用我们virtexultrascale+ vu19p设备的用户在十亿门设计上实现数mhz的性能。

cadence与xilinx前端到后端工作流程的紧密集成让软件工程师在开发最早期即可使用上述平台,将宝贵时间用于设计验证和软件开发,而不是耗时的原型验证初启。”

cadence验证全流程包括palladium z2硬件仿真加速系统、protium x2原型验证系统、xcelium logic simulation逻辑仿真器、jaspergold formal verification platform形式化验证平台以及cadence智能验证应用套件,可以提供最经济高效的验证吞吐率。

全新的palladium z2 和protium x2系统是cadence验证套件的组成部分,支持公司的智能系统设计(intelligent system design?)战略,助力实现soc卓越设计。palladium z2 和protium x2系统目前已在一些客户中成功部署,并将在2021年第二季度向业内广泛面世。如需了解更多有关palladium z2 和protium x2动力双剑组合的相关内容。

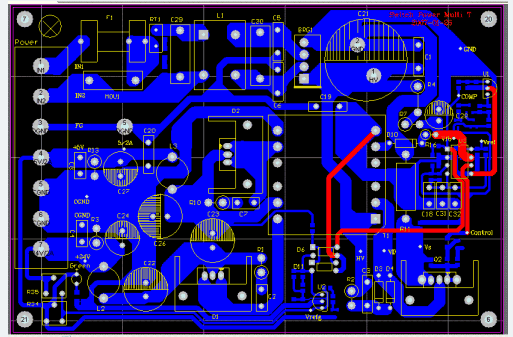

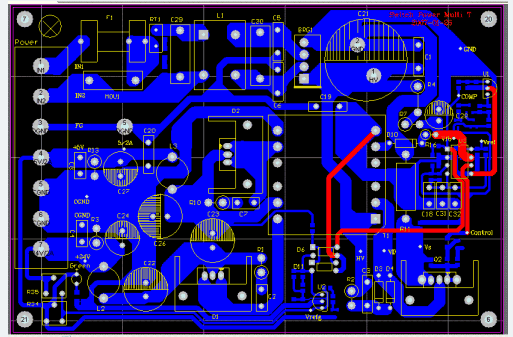

来源:华强电子网。图片供参考

关键词:arm v9架构 人工智能

楷登电子发布cadence palladium z2 enterprise emulation企业级硬件仿真加速系统和protium x2enterprise prototyping企业级原型验证系统,用于应对呈指数级上升的系统设计复杂度和上市时间的压力。

基于cadence原有的pallaidum z1和protiumx1产品,新一代系统为当前数十亿门规模的片上系统(soc)设计提供最佳的硅前硬件纠错效率和最高的软件调试吞吐率。

此双系统无缝集成统一的编译器和外设接口,双剑合璧,被称为系统动力双剑(dynamic duo)。

新一代系统基于下一代硬件仿真核心处理器和xilinx ultrascale+ vu19p fpga,将为客户带来2倍容量提升和1.5倍性能提升,以更少的时间为大规模芯片验证完成更多次数的迭代。

模块化编译技术也突破性地应用在两个系统中,使得100亿门的soc编译可以在palladium z2 系统10小时内即可完成,protium x2系统也仅需不到24小时就可以完成。

“我们对高端图形和超大规模设计的每一次升级都意味着复杂性的增加,上市时间也愈发紧张。”

nvidia公司硬件工程高级总监narendrakonda表示,

“采用结合cadence palladium z2和protium x2系统的通用前端流程,我们可以优化功能验证(verification)、功能确认(validation)和硅前软件初启的工作负载分布。得益于增加2倍的可用容量、提升50%的吞吐率以及更快的模块化编译循环,我们可以按时完成对最复杂gpu和soc设计的全面验证。”

palladium z2/protium x2 dynamic duo动力双剑组合被用于应对移动、消费电子和超大规模计算领域最先进应用设计所面临的挑战。

基于无缝集成的流程、统一的纠错、通用的虚拟和物理接口以及跨系统的测试平台内容,该动力双剑组合可以实现从硬件仿真到原型验证的快速设计迁移和测试。

“amd成功的重要成果之一,就是加速芯片开发流程并优化amd的左移战略。”

amd公司全球院士、方法学架构师alexstar说到,“采用cadence palladium z2 和 protium x2系统提升性能,在保证硬件仿真和原型验证间功能性一致的基础上,可以提升硅前工作负载的吞吐量。快速初启的能力以及在palladium z2硬件仿真与protiumx2原型验证间短时间切换能力,在开发最具挑战的soc设计时,为我们提供了优化自身的左移策略的机会。通过使用拥有业界领先的第三代amd epyc?处理器以及palladium z2和protium x2平台的资格认证的服务器,客户将能够将行业领先的性能计算带入palladium和protium生态系统。”

“先进soc设计的硅前验证需要具备数十亿门处理能力的解决方案,该方案须同时提供最高的性能以及快速可预测的纠错能力。”

cadence公司资深副总裁兼系统与验证事业部总经理paulcunningham表示,

“我们全新的dynamic duo动力双剑组合通过两个紧密集成的系统满足上述要求,包括针对快速可预测的硬件纠错优化的palladium z2硬件仿真加速系统,以及面向高性能数十亿门软件验证优化的protium x2原型验证系统。客户表达的强烈需求让我们深受鼓舞。cadence将继续与客户合作,利用新系统实现最高的设计验证吞吐率。”

“业界最佳的硬件仿真器是我们取得成功的关键,arm在基于arm的服务器上一直在广泛使用硬件仿真加速器和仿真工具,以实现最高的整体验证吞吐率。”

arm公司设计服务资深总监trannguyen表示,

“采用全新的cadencepalladiumz2系统,我们已经在最新设计上实现了超过50%的性能提升和2倍的容量增加,为我们提供了验证下一代ip和产品所需的强大的硅前验证能力。”

“xilinx与cadence紧密合作,确保cadence的软件前端能与后端的赛灵思vivado design suite设计套件无缝协作。”

xilinx公司关键应用市场资深总监hanneke krekels表示, “基于fpga的cadenceprotiumx2 原型验证平台让使用我们virtexultrascale+ vu19p设备的用户在十亿门设计上实现数mhz的性能。

cadence与xilinx前端到后端工作流程的紧密集成让软件工程师在开发最早期即可使用上述平台,将宝贵时间用于设计验证和软件开发,而不是耗时的原型验证初启。”

cadence验证全流程包括palladium z2硬件仿真加速系统、protium x2原型验证系统、xcelium logic simulation逻辑仿真器、jaspergold formal verification platform形式化验证平台以及cadence智能验证应用套件,可以提供最经济高效的验证吞吐率。

全新的palladium z2 和protium x2系统是cadence验证套件的组成部分,支持公司的智能系统设计(intelligent system design?)战略,助力实现soc卓越设计。palladium z2 和protium x2系统目前已在一些客户中成功部署,并将在2021年第二季度向业内广泛面世。如需了解更多有关palladium z2 和protium x2动力双剑组合的相关内容。

来源:华强电子网。图片供参考

公网安备44030402000607

公网安备44030402000607