处理器对从外面读入数据或是向外面输出数据的一个接口

发布时间:2023/7/30 12:00:13 访问次数:71

弹载计算机具有体积小、成本低、速度快、层叠结构等显著特点,并且单个模块融合多种接口。

信号处理器TMS320C6202B,最大工作频率250MHz,片上集成了3Mbit的数据/程序存储器SRAM、两路32位的定时器、EMIF总线接口、4路相互独立的DMA通道、3路MCBSP串行接口,内核采用1.5V供电,外围采用3.3V供电,封装为352芯BGA。

以ARM cortexA9 CPU做仿真实验,在CPU访存接口上挂一个理想的32位DDR模型(有访问请求立即响应,没有延时),CPU频率为1008MHz时,测得数据拷贝带宽为2140 MB/s。

一般会配置540MHz 32位DDR,能提供的理论带宽为4320MB/s,已经远超cortex-A9的带宽吞吐能力了,这种情况下带宽性能测试得到的只是CPU的访存性能,而不是DDR的总体带宽性能。 现在的带宽吞吐性能评测软件都是利用统计CPU访问DDR的速度来评估芯片总的带宽吞吐性能,这就需要考虑CPU Cache的影响。

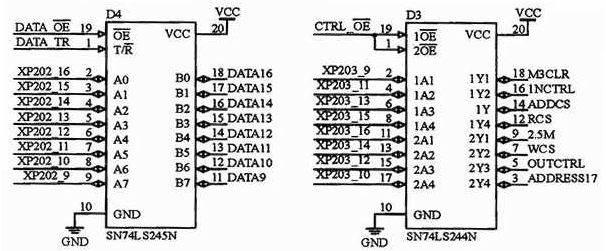

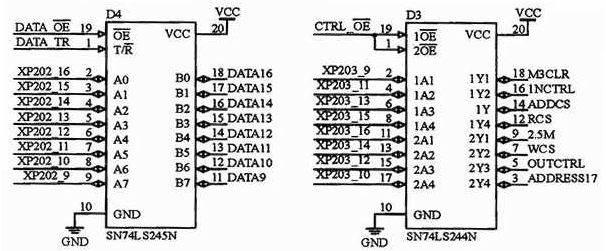

I/O端口存在读、写性问题,有的端口是只读的,有的端口是只写的,还有的端口是即可读也可写,其读写性是由外设芯片的寄存器所决定的,在芯片的数据手册中能找到。

存储器外设也存在I/O端口,以对其进行一定的控制。从I/O端口这一名字来看,对于处理器来说,就是对从外面读入数据或是向外面输出数据的一个接口总称。

与存储器外设所不同的是,I/O外设所点用的地址一般都很少。比如一个I/O外设可能存在多个控制寄存器,这些控制寄存器从处理器来看就是多个I/O端口(地址),向这个地址写数据就是向外设所对应的寄存器写数据,反之,也可以是读。

深圳市慈安科技有限公司http://cakj.51dzw.com

弹载计算机具有体积小、成本低、速度快、层叠结构等显著特点,并且单个模块融合多种接口。

信号处理器TMS320C6202B,最大工作频率250MHz,片上集成了3Mbit的数据/程序存储器SRAM、两路32位的定时器、EMIF总线接口、4路相互独立的DMA通道、3路MCBSP串行接口,内核采用1.5V供电,外围采用3.3V供电,封装为352芯BGA。

以ARM cortexA9 CPU做仿真实验,在CPU访存接口上挂一个理想的32位DDR模型(有访问请求立即响应,没有延时),CPU频率为1008MHz时,测得数据拷贝带宽为2140 MB/s。

一般会配置540MHz 32位DDR,能提供的理论带宽为4320MB/s,已经远超cortex-A9的带宽吞吐能力了,这种情况下带宽性能测试得到的只是CPU的访存性能,而不是DDR的总体带宽性能。 现在的带宽吞吐性能评测软件都是利用统计CPU访问DDR的速度来评估芯片总的带宽吞吐性能,这就需要考虑CPU Cache的影响。

I/O端口存在读、写性问题,有的端口是只读的,有的端口是只写的,还有的端口是即可读也可写,其读写性是由外设芯片的寄存器所决定的,在芯片的数据手册中能找到。

存储器外设也存在I/O端口,以对其进行一定的控制。从I/O端口这一名字来看,对于处理器来说,就是对从外面读入数据或是向外面输出数据的一个接口总称。

与存储器外设所不同的是,I/O外设所点用的地址一般都很少。比如一个I/O外设可能存在多个控制寄存器,这些控制寄存器从处理器来看就是多个I/O端口(地址),向这个地址写数据就是向外设所对应的寄存器写数据,反之,也可以是读。

深圳市慈安科技有限公司http://cakj.51dzw.com

公网安备44030402000607

公网安备44030402000607