精密微型微机电系统惯性测量单元

发布时间:2020/5/21 20:35:06 访问次数:1465

RC0603JR07120R计算密集型网关和边缘设备的趋势正在推动传统确定性控制应用程序与额外嵌入式处理功能的集成需求,后者是开发智能安全连接系统所必须的组件。针对这一需求,Microchip Technology Inc.(美国微芯科技公司)启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。新产品依托屡获殊荣的中等密度PolarFire FPGA系列产品打造而成,提供全球首款基于RISC-V的强化型实时微处理器子系统,同时支持Linux操作系统,为嵌入式系统带来一流的低功耗、热效率和防御级安全性。

符合要求的EAP客户可立即使用Microchip的Libero SoC 12.3 FPGA设计工具包和SoftConsole 6.2集成开发环境(适用于嵌入式开发人员)进行设计。客户现在还可以使用Renode调试其嵌入式应用程序,Renode是微处理器子系统的一个虚拟模型。

FPGA加速的关键因素,Xilinx Ultrascale系列FPGA运行的最高频率在300MHz到400MHz之间,但DSP是FPGA中的硬核,可以运行在更高的频率上。SLB-M与DSP这样构成的基本单元,被称之为Supertile,FPGA内部Supertile的布局如图3所示。Supertile技术的核心在于使DSP运行于两倍逻辑频率上,使整个系统算力达到倍增的效果。这主要得益于芯片结构中SLICEM与DSP位置临近,使用专有的布线资源,延迟缩短,可以支撑SLICEM以双倍逻辑运行的频率向DSP提供数据。另外,神经网络中存在着数据复用,通过filter和image数据的复用和交织,一次取数多次使用,从而减少数据的搬运次数,提升计算效率。

利用DSP48E2的结构特点,一个DSP完成两路INT8的乘加。在进行8bit数据计算时,将a左移18位,置于输入的高8位,低19位补0,从DSP的A端输入,b维持在低8位,从DSP的D端输入,a与b两者先进行累加,然后与c相乘后,结果将分别位于输出的高(a*c)、低(b*c)两部分,在实践中,我们把a,b两路作为filter数据输入,c作为image数据输入。这样DSP在一个时钟周期内就同时完成了两路的计算,再次使算力翻倍。结合前面提到的supertile倍频设计,两种设计使得单个DSP的算力提升四倍。因为一次计算过程有乘、加两个操作(operations),所以单个DSP在一个时钟周期高效的完成了8个operations。

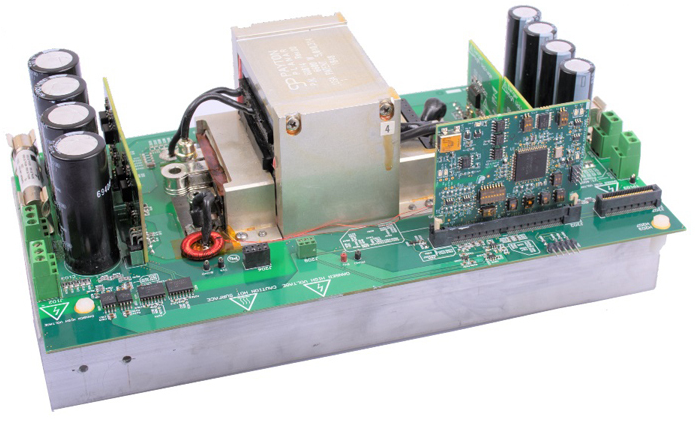

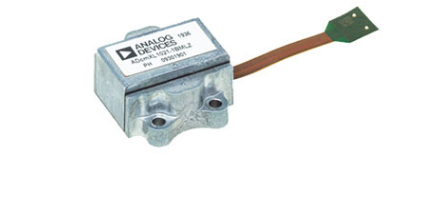

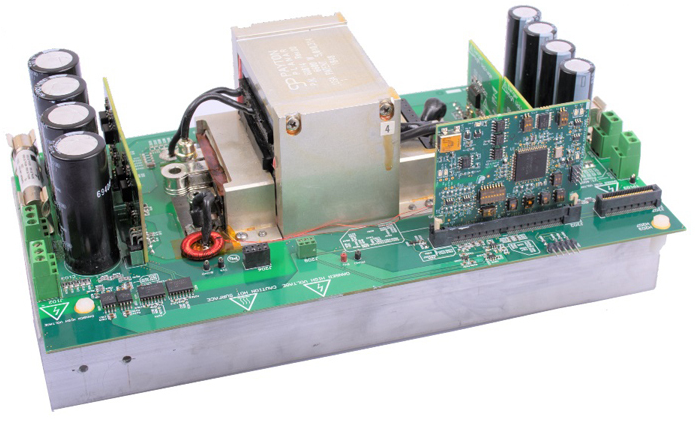

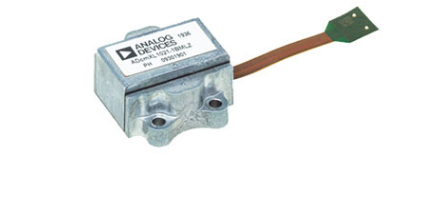

Analog Devices Inc. ADIS16505精密微型微机电系统 (MEMS) 惯性测量单元 (IMU) 包括一个三轴陀螺仪和一个三轴加速度计。ADIS16505提供了一种简单且经济高效的方法,用于将精确的多轴惯性检测技术集成到工业系统中。ADIS16505 MEMS IMU设有惯性传感器,结合了可优化动态性能的信号调理功能。工厂校准可表现每个传感器的灵敏度、偏置、对准、线性加速(陀螺仪偏置)和冲击点(加速度计位置)。因此,每个传感器都有动态补偿公式,用于在各种条件下提供准确的传感器测量。

所有必要的运动检测和校准均已在工厂生产过程中完成,大大缩短了系统集成时间。在导航系统中,紧密的正交对准简化了惯性坐标系对准。串行外设接口 (SPI) 和寄存器结构设有一个简单接口,用于数据收集和配置控制。

ADIS16505采用100焊球球栅阵列 (BGA) 封装,尺寸约为15mm × 15mm × 5mm。特性三轴数字陀螺仪±125°/s、±500°/s、±2000°/s动态范围型号运行偏置稳定性为2.3°/h (ADIS16505-1)x轴和y轴角度随机游走为0.13°/√h,1σ (ADIS16505-1)轴间错位误差为±0.25°三轴数字加速度计,动态范围为±78.4m/s226.5μm/s2运行偏置稳定性(x轴和y轴)三轴、角度增量和速度增量输出SPI兼容数据通信。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

RC0603JR07120R计算密集型网关和边缘设备的趋势正在推动传统确定性控制应用程序与额外嵌入式处理功能的集成需求,后者是开发智能安全连接系统所必须的组件。针对这一需求,Microchip Technology Inc.(美国微芯科技公司)启动了PolarFire片上系统(SoC)现场可编程门阵列(FPGA)早期使用计划(EAP)。新产品依托屡获殊荣的中等密度PolarFire FPGA系列产品打造而成,提供全球首款基于RISC-V的强化型实时微处理器子系统,同时支持Linux操作系统,为嵌入式系统带来一流的低功耗、热效率和防御级安全性。

符合要求的EAP客户可立即使用Microchip的Libero SoC 12.3 FPGA设计工具包和SoftConsole 6.2集成开发环境(适用于嵌入式开发人员)进行设计。客户现在还可以使用Renode调试其嵌入式应用程序,Renode是微处理器子系统的一个虚拟模型。

FPGA加速的关键因素,Xilinx Ultrascale系列FPGA运行的最高频率在300MHz到400MHz之间,但DSP是FPGA中的硬核,可以运行在更高的频率上。SLB-M与DSP这样构成的基本单元,被称之为Supertile,FPGA内部Supertile的布局如图3所示。Supertile技术的核心在于使DSP运行于两倍逻辑频率上,使整个系统算力达到倍增的效果。这主要得益于芯片结构中SLICEM与DSP位置临近,使用专有的布线资源,延迟缩短,可以支撑SLICEM以双倍逻辑运行的频率向DSP提供数据。另外,神经网络中存在着数据复用,通过filter和image数据的复用和交织,一次取数多次使用,从而减少数据的搬运次数,提升计算效率。

利用DSP48E2的结构特点,一个DSP完成两路INT8的乘加。在进行8bit数据计算时,将a左移18位,置于输入的高8位,低19位补0,从DSP的A端输入,b维持在低8位,从DSP的D端输入,a与b两者先进行累加,然后与c相乘后,结果将分别位于输出的高(a*c)、低(b*c)两部分,在实践中,我们把a,b两路作为filter数据输入,c作为image数据输入。这样DSP在一个时钟周期内就同时完成了两路的计算,再次使算力翻倍。结合前面提到的supertile倍频设计,两种设计使得单个DSP的算力提升四倍。因为一次计算过程有乘、加两个操作(operations),所以单个DSP在一个时钟周期高效的完成了8个operations。

Analog Devices Inc. ADIS16505精密微型微机电系统 (MEMS) 惯性测量单元 (IMU) 包括一个三轴陀螺仪和一个三轴加速度计。ADIS16505提供了一种简单且经济高效的方法,用于将精确的多轴惯性检测技术集成到工业系统中。ADIS16505 MEMS IMU设有惯性传感器,结合了可优化动态性能的信号调理功能。工厂校准可表现每个传感器的灵敏度、偏置、对准、线性加速(陀螺仪偏置)和冲击点(加速度计位置)。因此,每个传感器都有动态补偿公式,用于在各种条件下提供准确的传感器测量。

所有必要的运动检测和校准均已在工厂生产过程中完成,大大缩短了系统集成时间。在导航系统中,紧密的正交对准简化了惯性坐标系对准。串行外设接口 (SPI) 和寄存器结构设有一个简单接口,用于数据收集和配置控制。

ADIS16505采用100焊球球栅阵列 (BGA) 封装,尺寸约为15mm × 15mm × 5mm。特性三轴数字陀螺仪±125°/s、±500°/s、±2000°/s动态范围型号运行偏置稳定性为2.3°/h (ADIS16505-1)x轴和y轴角度随机游走为0.13°/√h,1σ (ADIS16505-1)轴间错位误差为±0.25°三轴数字加速度计,动态范围为±78.4m/s226.5μm/s2运行偏置稳定性(x轴和y轴)三轴、角度增量和速度增量输出SPI兼容数据通信。

(素材来源:ttic和eechina.如涉版权请联系删除。特别感谢)

上一篇:指数型运算比较耗资源

公网安备44030402000607

公网安备44030402000607