12102C473KAT2A 异步清零和暂停计数的功能

发布时间:2019/10/20 15:55:39 访问次数:1125

12102C473KAT2A出图2所示4写步置数、加计数、减即当计数器递增计电路编码,画出状态图

(注意考产生一个高时,产生一模8、模10和模12在s和6,6.3所示,并要求具有异步清零和暂停计数的功能。表题6,6,3 计数器的模数控制表数状态;当CR为高电平但EⅣ为停计数。

低电平时,计数器暂6,6,5 某电路的状态图如图题6.6,5所示,图中,跖为控制变量,当″=0时,电路按顺时针方向所指的状态进行转换;当跖=1时,则按反时针方向进行状态转换。试用Vcrilog描述该电路。一个序列检测器4位二检测歪计数,其模数该,输出图题6.

要求该计数器带有复位端CR和计数控制端EⅣ其输出为1;当CR和EⅣ均为高电平时,计数器处于计数状态;当CR为高电平但EⅣ为低电平时,计数器暂,在S

6.6.3所示,并要求具有异步清零和表题6,6,3 计数器的模数控制表器件示的0LMC后又从1开始,周而复始运行。计数器的。当CR为低电平时,计数器复位,

同步模5、模暂停计数的功能。位信号Co;相6.7.1厄)=1, XOR(时的等效模10

模12计数图题6,6.5控制信号⑦坚控制信号模5计数模8计数.

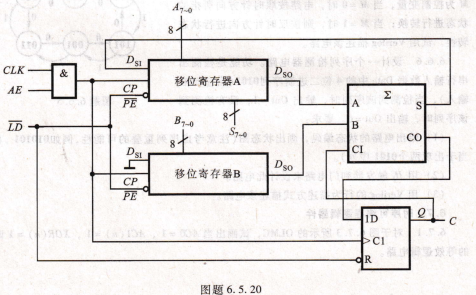

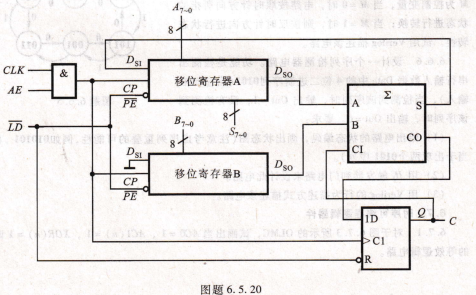

当AE=1时,进行串行加法运算,输人8个时钟脉冲后恢复为0;s7~0为8位和输出端;C

为进位输出端。移位寄存器A、B的CP端为时钟输人端,P召端为并行置数控制端,DsI和人端、输出端。试分析电路的工作原理。

12102C473KAT2A出图2所示4写步置数、加计数、减即当计数器递增计电路编码,画出状态图

(注意考产生一个高时,产生一模8、模10和模12在s和6,6.3所示,并要求具有异步清零和暂停计数的功能。表题6,6,3 计数器的模数控制表数状态;当CR为高电平但EⅣ为停计数。

低电平时,计数器暂6,6,5 某电路的状态图如图题6.6,5所示,图中,跖为控制变量,当″=0时,电路按顺时针方向所指的状态进行转换;当跖=1时,则按反时针方向进行状态转换。试用Vcrilog描述该电路。一个序列检测器4位二检测歪计数,其模数该,输出图题6.

要求该计数器带有复位端CR和计数控制端EⅣ其输出为1;当CR和EⅣ均为高电平时,计数器处于计数状态;当CR为高电平但EⅣ为低电平时,计数器暂,在S

6.6.3所示,并要求具有异步清零和表题6,6,3 计数器的模数控制表器件示的0LMC后又从1开始,周而复始运行。计数器的。当CR为低电平时,计数器复位,

同步模5、模暂停计数的功能。位信号Co;相6.7.1厄)=1, XOR(时的等效模10

模12计数图题6,6.5控制信号⑦坚控制信号模5计数模8计数.

当AE=1时,进行串行加法运算,输人8个时钟脉冲后恢复为0;s7~0为8位和输出端;C

为进位输出端。移位寄存器A、B的CP端为时钟输人端,P召端为并行置数控制端,DsI和人端、输出端。试分析电路的工作原理。

上一篇:89051T电路输出z的序列

上一篇:YLB2785 复杂可编程器件

公网安备44030402000607

公网安备44030402000607