MBR0520LT3вьВНжУСуЙІФмЕФDДЅЗЂЦї

ЗЂВМЪБМф:2019/10/19 16:42:31 ЗУЮЪДЮЪ§:1137

MBR0520LT3МЦЪ§ЦїЕФVerilogНЈФЃ

ЯТУцЭЈЙ§3ИіЪЕР§НщЩмЭЌВНЖўНјжЦМЦЪ§ЦїЁЂвьВНЖўНјжЦМЦЪ§ЦїКЭЗЧЖўНјжЦМЦЪ§ЦїЕФVernogНЈФЃЁЃ

ЭЌВНЖўНјжЦМЦЪ§Цї,Р§6.6.2жаЕФФЃПщУшЪіСЫОпгавьВНжУСуЁЂВЂаажУЪ§ЙІФмЕФ4ЮЛЭЌВНЖўНјжЦМЦЪ§Цї,ЭъГЩЕФЙІФмгыЭМ6.5.13ЫљЪО74LVC161РрЫЦЁЃдкИУФЃПщжаЛьКЯЪЙгУСЫassignгяОфКЭalwaysгяОф,assignгяОфУшЪіСЫзщКЯЕчТЗжагЩгыУХВњЩњЕФЪЙФмПижЦаХКХCE(жаМфНкЕу)КЭНјЮЛЪфГіаХКХTC,ЕБМЦЪ§ЦїМЦЪ§ЕНзюДѓжЕ15ЪБ,TC=1ЁЃИљОнБэ6.5,6,alwaysгяОфУшЪіСЫМЦЪ§ЦїЕФТпМЙІФм,ЕБCRаХКХЬјБфЕНЕЭЕчЦН(гЩnegedge CRУшЪі)ЪБ,МЦЪ§ЦїЕФЪфГіБЛжУСу;Зёдђ,ЕБCR=1ЪБ,дкCPЕФЩЯЩ§бизїгУЯТ,ЭъГЩЦфЫћШ§жжЙІФм:ЭЌВНжУЪ§ЁЂМг1МЦЪ§КЭБЃГждгазДЬЌВЛБфЁЃзЂвт,iF-elseгяОфвўКЌЕФгХЯШМЖБ№гыБэ6.5.6ЯрЭЌЁЃ

Р§6,6.2

///ЁУBinary counterЁЂVith para11el load and enable

//see Figure 6.5.13 andЁфrable 6.5.6

1nodule counter74x161 (CEP, CET,PE, D, CP, CR, Q,TC);

input CEP, CET,PE, CP, CR;

input[3:0]D; //Data input

output TC; //C)utput carry

output[3:0]Q; //DataЁЃutput

reg[3:0]Q;

w1re CE;

assign CE = CEP&I CET;

assign TC=CET&(Q・==4ЁЏb1111);

always@(posedge CP or negedge CR)

iF(~CR)Q <=4ЁЏb0000;

ense if( ~PE)Q<=D.; //PE=0, synchronous load input

else iF(~CE)Q<=Q; //the output no change

else Q(=Q+1i bl;

endmodule

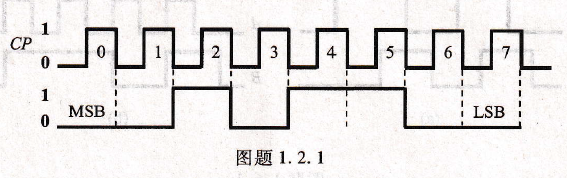

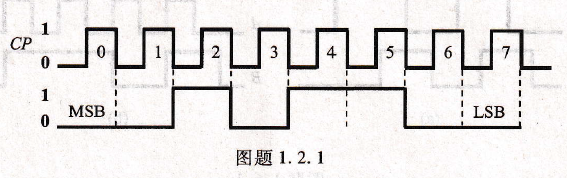

вьВНЖўНјжЦМЦЪ§Цї,вьВНМЦЪ§ЦїЕФНсЙЙЛЏУшЪіШчР§6.6.3ЫљЪОЁЃЕквЛИіФЃПщЭЈЙ§4ДЮЕїгУЕкЖўИіФЃПщЭъГЩМЦЪ§ЙІФм,ЕкЖўИіФЃПщЪЧДјгавьВНжУСуЙІФмЕФDДЅЗЂЦїзїЮЊЩшМЦЕФЕзВуЁЃдкЕквЛИіФЃПщжа,Ек1ИіДЅЗЂЦїFFOЕФЪфГіQ0ОЗДЯр(гУ~Q0БэЪО)КѓгыDЪфШыЯрСЌ(дкFFOжагУ~Q0ШЁДњD),ЙЙГЩrЁфДЅЗЂЦї,ЦфЪБжгНгЕНЭтВПЪфШЫCPЁЃЕк2ИіДЅЗЂЦїF1ЕФЪфГіQ1ОЗДЯрКѓгыDЪфШЫЯрСЌ(дкFF1жагУ~Q1ШЁДњD),ЦфЪБжгНгЕНЧАвЛИіДЅЗЂЦїЕФЪфГі(гУQ0ШЁДњCP)ЁЃРрЫЦЕи,НЋ4ИіДЅЗЂЦїМЖСЊдквЛЦ№ЙЙГЩвьВНЖўНјжЦМЦЪ§Цї,ЦфдРэЭМгыЭМ6.5.8РрЫЦЁЃашвЊзЂвтЕФЪЧ,ЕїгУЕкЖўИіФЃПщЪБЖЫПкЕФХХСаЫГађЁЃ

Р§6.6,3

//Ripple counter(Refer to Fig.6.5.8)

module ripplecounter(Q0,Q1,Q2,Q3,CP,CR);

output Q0,Q1,Q2,Q3;

input CP,CR;

//Instantiate D nip-nЁЃp

D~FF FFO(Q0,~Q0,CP,~CR);

D FF FF1

D FF FF2

D FF FF3

endmodule

Q1,~Q1,Q0,~CR);

Q2,~Q2,Q1,~CR);

Q3,~Q3,Q2,~CR);

l`9

//module I)~FFЁЂvith asynchronous reset

lllodule D~FF(Q,D,CP,Rd);

output Q;

input D,CP,R-;

reg Q;

always@( negedge CP or negedge Rd)

if(~Rd)Q<=1ЁЏbO;

else Q(=D;

MBR0520LT3МЦЪ§ЦїЕФVerilogНЈФЃ

ЯТУцЭЈЙ§3ИіЪЕР§НщЩмЭЌВНЖўНјжЦМЦЪ§ЦїЁЂвьВНЖўНјжЦМЦЪ§ЦїКЭЗЧЖўНјжЦМЦЪ§ЦїЕФVernogНЈФЃЁЃ

ЭЌВНЖўНјжЦМЦЪ§Цї,Р§6.6.2жаЕФФЃПщУшЪіСЫОпгавьВНжУСуЁЂВЂаажУЪ§ЙІФмЕФ4ЮЛЭЌВНЖўНјжЦМЦЪ§Цї,ЭъГЩЕФЙІФмгыЭМ6.5.13ЫљЪО74LVC161РрЫЦЁЃдкИУФЃПщжаЛьКЯЪЙгУСЫassignгяОфКЭalwaysгяОф,assignгяОфУшЪіСЫзщКЯЕчТЗжагЩгыУХВњЩњЕФЪЙФмПижЦаХКХCE(жаМфНкЕу)КЭНјЮЛЪфГіаХКХTC,ЕБМЦЪ§ЦїМЦЪ§ЕНзюДѓжЕ15ЪБ,TC=1ЁЃИљОнБэ6.5,6,alwaysгяОфУшЪіСЫМЦЪ§ЦїЕФТпМЙІФм,ЕБCRаХКХЬјБфЕНЕЭЕчЦН(гЩnegedge CRУшЪі)ЪБ,МЦЪ§ЦїЕФЪфГіБЛжУСу;Зёдђ,ЕБCR=1ЪБ,дкCPЕФЩЯЩ§бизїгУЯТ,ЭъГЩЦфЫћШ§жжЙІФм:ЭЌВНжУЪ§ЁЂМг1МЦЪ§КЭБЃГждгазДЬЌВЛБфЁЃзЂвт,iF-elseгяОфвўКЌЕФгХЯШМЖБ№гыБэ6.5.6ЯрЭЌЁЃ

Р§6,6.2

///ЁУBinary counterЁЂVith para11el load and enable

//see Figure 6.5.13 andЁфrable 6.5.6

1nodule counter74x161 (CEP, CET,PE, D, CP, CR, Q,TC);

input CEP, CET,PE, CP, CR;

input[3:0]D; //Data input

output TC; //C)utput carry

output[3:0]Q; //DataЁЃutput

reg[3:0]Q;

w1re CE;

assign CE = CEP&I CET;

assign TC=CET&(Q・==4ЁЏb1111);

always@(posedge CP or negedge CR)

iF(~CR)Q <=4ЁЏb0000;

ense if( ~PE)Q<=D.; //PE=0, synchronous load input

else iF(~CE)Q<=Q; //the output no change

else Q(=Q+1i bl;

endmodule

вьВНЖўНјжЦМЦЪ§Цї,вьВНМЦЪ§ЦїЕФНсЙЙЛЏУшЪіШчР§6.6.3ЫљЪОЁЃЕквЛИіФЃПщЭЈЙ§4ДЮЕїгУЕкЖўИіФЃПщЭъГЩМЦЪ§ЙІФм,ЕкЖўИіФЃПщЪЧДјгавьВНжУСуЙІФмЕФDДЅЗЂЦїзїЮЊЩшМЦЕФЕзВуЁЃдкЕквЛИіФЃПщжа,Ек1ИіДЅЗЂЦїFFOЕФЪфГіQ0ОЗДЯр(гУ~Q0БэЪО)КѓгыDЪфШыЯрСЌ(дкFFOжагУ~Q0ШЁДњD),ЙЙГЩrЁфДЅЗЂЦї,ЦфЪБжгНгЕНЭтВПЪфШЫCPЁЃЕк2ИіДЅЗЂЦїF1ЕФЪфГіQ1ОЗДЯрКѓгыDЪфШЫЯрСЌ(дкFF1жагУ~Q1ШЁДњD),ЦфЪБжгНгЕНЧАвЛИіДЅЗЂЦїЕФЪфГі(гУQ0ШЁДњCP)ЁЃРрЫЦЕи,НЋ4ИіДЅЗЂЦїМЖСЊдквЛЦ№ЙЙГЩвьВНЖўНјжЦМЦЪ§Цї,ЦфдРэЭМгыЭМ6.5.8РрЫЦЁЃашвЊзЂвтЕФЪЧ,ЕїгУЕкЖўИіФЃПщЪБЖЫПкЕФХХСаЫГађЁЃ

Р§6.6,3

//Ripple counter(Refer to Fig.6.5.8)

module ripplecounter(Q0,Q1,Q2,Q3,CP,CR);

output Q0,Q1,Q2,Q3;

input CP,CR;

//Instantiate D nip-nЁЃp

D~FF FFO(Q0,~Q0,CP,~CR);

D FF FF1

D FF FF2

D FF FF3

endmodule

Q1,~Q1,Q0,~CR);

Q2,~Q2,Q1,~CR);

Q3,~Q3,Q2,~CR);

l`9

//module I)~FFЁЂvith asynchronous reset

lllodule D~FF(Q,D,CP,Rd);

output Q;

input D,CP,R-;

reg Q;

always@( negedge CP or negedge Rd)

if(~Rd)Q<=1ЁЏbO;

else Q(=D;

ЩЯвЛЦЊЃКFBL-VN1-LL01-0вЦЮЛМФДцЦїЕФVerilogНЈФЃ

ЩЯвЛЦЊЃКPSN0503083ЭЌВНЪЎНјжЦМЦЪ§Цї

ШШУХЕуЛї

ШШУХЕуЛї

- Arduino UnoПижЦЦїАхЬсЙЉ5VЪфГі

- дТЯраЮГЩдРэЭМЁБЩЯЫљЪОдТЧђ

- Ъ§зжЪНЭђгУБэШчКЮВтЕчзшЁЂНЛжБСїЕчбЙЁЂжБСїЕчСї

- ЪЕгУаТаЭЩцМАLEDЕЦЩшБИММЪѕСьгђ

- OLEDЕчЪгдкШЋЧђЪаГЁЧАОАЙуРЋ

- ЖдiPad miniЕФЩ§МЖжЎзїХЮЭћвбОУ

- ЮжЛЅЖЏТМВЅВЩгУAll in oneЕФЩшМЦ

- ДгТЗЮШбЙЪфГіЕїНка§ХЅ

- SK55GARL065E ЫЋЩуЯёЭЗ+ 6жжбе

- аТЭўЭЈаХMPIЬьЯпНјеЙВЛЫГРћ

ЭЦМіММЪѕзЪСЯ

ЭЦМіММЪѕзЪСЯ

- жаЙњДЋУНДѓбЇДЋУНВЉЮяЙнПЊ

- ДЋУНВЉЮяЙнПЊЙнвЧЪНТЁЭЏОйааЁЃНЬг§ЖМiЙњМвЙуЕчзмОжЕШВПУХ... [ЯъЯИ]

- аТвЛДњцчСњ8ЯЕСаЦьНЂаОЦЌгІгУбаОП

- гадДИпЭЈТЫВЈЦї(RC4558DN)гІгУЯъНт

- WTC6216ДЅУўЪНАДМќЩшМЦгІ

- жаЧЖШыЪНДцДЂЦїASICКЭSoCЩшМЦЬиЕугХЪЦ

- 16VЁЂ8A Silent Switcher

- МЏГЩЦЅХфТЫВЈаОЦЌ

- ЖрУНЬхаДІРэЦїSM501дкЧЖШыЪНЯЕЭГжаЕФгІгУ

- ЛљгкIEEE802.11bЕФEPAЮТЖШБфЫЭЦї

- QUICCEngineаТв§ЧцЭЦЖЏIPЭјТчИяаТ

- SoCУцЪРАЫФъКѓЕФВњвЕЛњгі

- MPC8xxЯЕСаДІРэЦїЕФЧЖШыЪНЯЕЭГЕчдДЩшМЦ

- dsPICМАЦфдкНЛСїБфЦЕЕїЫйжаЕФгІгУбаОП

ЙЋЭјАВБИ44030402000607

ЙЋЭјАВБИ44030402000607