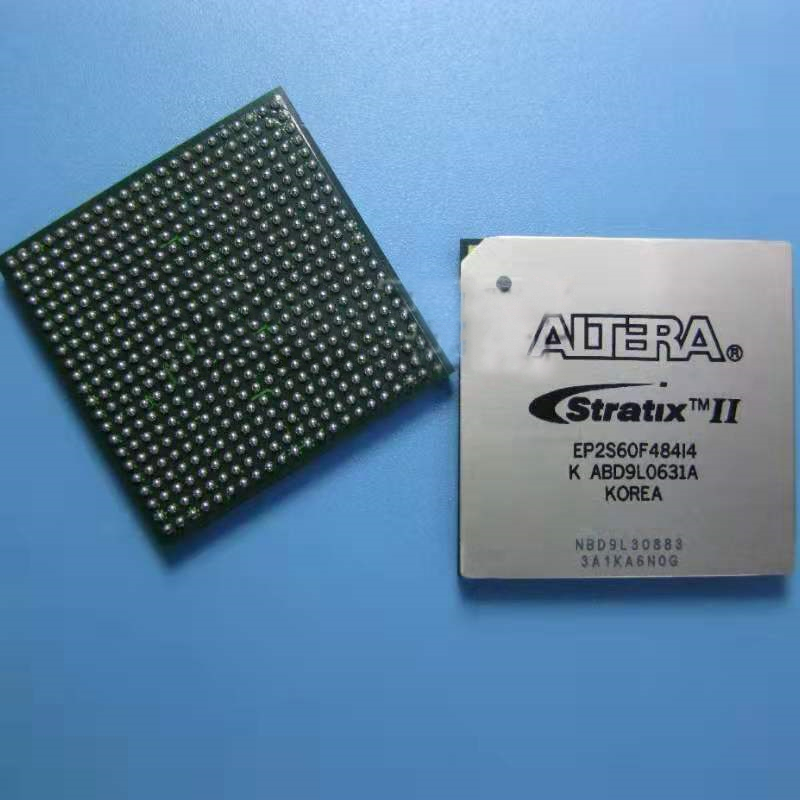

介绍:EP2S60F484I4N

Stratix®II FPGA系列基于1.2V,90nm全层铜SRAM工艺并具有新的逻辑结构,可最大程度地发挥作用性能,并使设备密度接近18万

等效逻辑元素(LE)。 Stratix II器件提供高达9 Mbit的片上TriMatrix™存储器,用于要求苛刻的存储器密集型应用程序,并具有多达96个DSP模块和多达384个(18位×18位)

有效实现高性能滤波器的乘法器其他DSP功能。各种高速外部存储器接口是支持,包括双倍数据速率(DDR)SDRAM和DDR2

SDRAM,RLDRAM II,四倍数据速率(QDR)II SRAM和单数据速率(SDR)SDRAM。 Stratix II器件支持各种I / O标准以及对每秒1 Gb(Gbps)源同步的支持

用DPA电路发信号。 Stratix II器件提供完整的时钟内部时钟频率高达550 MHz的管理解决方案以及多达12个锁相环(PLL)。 Stratix II器件也是

业界首款能够解密配置的FPGA使用高级加密标准(AES)算法的比特流保护设计。

特征:EP2S60F484I4N

Stratix II系列提供以下功能:

■15,600至179,400个等效LE;见表1-1

■新的和创新的自适应逻辑模块(ALM),基本

Stratix II架构的构建块,使性能最大化

和资源使用效率

■多达9,383,040个RAM位(1,172,880字节)可用而无

减少逻辑资源

■TriMatrixmemory由三个要实现的RAM块大小组成

真正的双端口内存和先进先出(FIFO)缓冲区

■高速DSP模块提供了专用的实现

乘法器(最高450 MHz),乘法累加函数和

有限脉冲响应(FIR)滤波器

■多达16个全局时钟,每个设备区域具有24个时钟资源

■时钟控制模块支持启用/禁用动态时钟网络,

允许时钟网络掉电以减少功率

用户模式下的消费

■每个设备最多12个PLL(四个增强型PLL和八个快速PLL)

提供扩频,可编程带宽,时钟切换,实时PLL重配置和高级乘法

和相移

■支持多种单端和差分I / O标准

■通过DPA电路实现1 Gbps的高速差分I / O支持

性能

■支持高速网络和通信总线

标准,包括并行RapidIO,SPI-4第2阶段(POS-PHY

4级),HyperTransport™技术和SFI-4

■支持高速外部存储器,包括DDR和DDR2

SDRAM,RLDRAM II,QDR II SRAM和SDR SDRAM

■支持以下多种知识产权宏功能

AlteraMegaCore®功能和Altera Megafunction合作伙伴

程序(AMPPSM)宏功能

■使用配置比特流支持设计安全性

加密

■支持远程配置更新

制造商:EP2S60F484I4N

Intel

产品种类:

FPGA - 现场可编程门阵列

发货限制:

Mouser 目前在您所在地区不销售该产品。

RoHS:

详细信息

产品:

Stratix II

逻辑元件数量:

60440

逻辑数组块数量――LAB:

3022

输入/输出端数量:

334 I/O

工作电源电压:

1.2 V

最小工作温度:

- 40 C

最大工作温度:

+ 85 C

安装风格:

SMD/SMT

封装 / 箱体:

FBGA-484

封装:

Tray

系列:

Stratix II EP2S60

商标:

Intel / Altera

湿度敏感性:

Yes

工作电源电流:

500 mA

产品类型:

FPGA - Field Programmable Gate Array

工厂包装数量:

60

子类别:

Programmable Logic ICs

总内存:

2544192 bit

商标名:

Stratix II