���ڻ���������ս�Ͳ������أ�����Ħ�����ɶԵ�Ƭ���ɵ�·�ܶȵ������ٶ��Ѿ��Ż���Ȼ�����Ӽܹ��ĽǶ����������ճ�Ʒ����Ķ��������ڲ������������ڲ����µ��칹������Ԫ���Ż�������Ϊ���ĵ�Ӧ�ó����ǣ���ͳ�Ĵ�����-�ڴ�ӿ��ӳ��谭����ЩӦ����������ܲ���������Semiwiki���϶��߶Ը���оƬ��װ��Ʒ�����½�չ�Ѿ��������ţ�Ҳ���ǻ���2.5D���н��ͻ���3D��ͨ�����ˡ�

Ȼ�������ٶ�����˵������������ǣ���Щ��Ʒ�ᱻ��Ѹ�ٵĽ��ܣ��Լ��ͻ�����μ�����������Ƽܹ��Ķ�оƬ���Ͽռ䡣��������л���μ���Ӣ�ض�(INTC.US)�ٰ�ĸ���װ���ֻᣬ�������Ϊ��ҵ��Ը�MCP��Ƶļƻ���������١�

�����ֻ��ϣ������������չ������עĿ�ļ�����Ӣ�ض���װ/���Լ�������(ATTD)���ܲ�Ram Viswanath�ķ��ԣ���˵"���ǿ����˶��ص�3D��2.5D��װ�������������ǿ�����ͻ���������Ʒ�ܹ�ʦ���������������ǰ��δ�еĹ�ģ���ܶ����Ե�MCP��"���dz������ϵķ��ԣ�һЩ��Ա����Ҫ��Ram����ȷ�ϡ���ӹ���ɣ����������İ뵼��IDM���������ͻ�һ��Ѱ��MCP��ƺ�����

���磬����ĸ���ͼ�����˰�CPU��GPU��VR�������ʹ洢���ܹ���װ��һ����ռԭ����Ԫ����װ��������֮һ��С�Ŀռ䣬ԭ��װ�ijߴ��п��ܴܺ�-��ߴ�100mm x100mm��(Ӣ�ض�Xeonϵ�е�Cascade Lake������ģ����һ��76mm x72.5mm��MCP����������"ȫ�̶ȳߴ�"������оƬ��)

���ڱ��صĶ�����˵������ǰ��ʱ��Ӣ�ض������ո��Ĵ�������������ĸо�����ȫ��ͬ�ġ����ﴫ����һ�������ģ�������Ҫ����Ϣ-���˵���������Ӧ�ó������ö�оƬ��װ���ɼ���(Χ��Ӣ�ض�CPU��FPGA)��Ӣ�ض�ATTDҵ���Ż�������֧����Щ���صĿͻ���ơ�

���潫����һЩӢ�ض�MCP����ʷ����2.5D��3D��װ������ϸ�ڣ��Լ�һЩ���ڽ����еĶ�δ����װ�������о�

MCP History

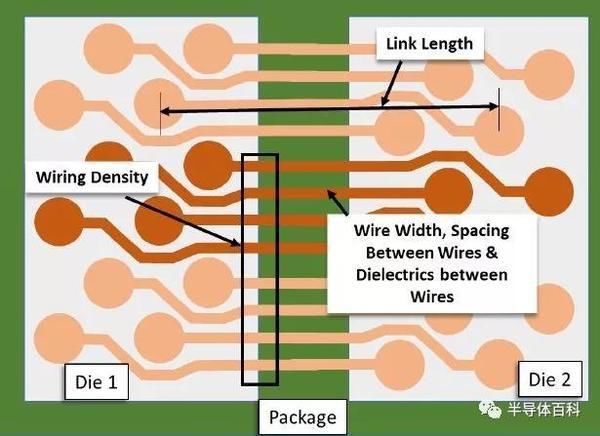

���ֻ�������������Ram V.������Ӣ�ض�MCP�������з��зḻ�ļ��⡣��˵��"Ӣ�ض��ڶ�оƬ��װ����ӵ�д����ľ��顣���磬���������Ƴ�һ���һ����Ƕ��ʽ���ż���������оƬ���װ���ӣ��Ѿ��з���ʮ���ꡣ���ּ���������оƬ����ӿ����ӣ��Ҿ��е�pJ/λ���ģ��Լ�оƬ����ź���ĺ͵ͳɱ������ԡ�"��ͼ���������оƬ��Ե��bump��֮��Ļ�������-һ���ؼ�ָ����(bump���ܶȺ�ƽ��die�ܳ��ڿ����ߵļ��߳���)

�������������ص��ǽ�����Ƕ����������л���װ��װ�����С��Ž��ߵ�λ�úͽǶ�Ҫ��dz����̡�����Ram����˵����

Ramչʾ�˲���Ƕ��ʽ�Ž����Ĵ���HBM�ڴ��Stratix FPGAģ���ʾ�������˲�Ʒ·��ͼʼ��Ӣ�ض����չ�֮ǰ����Altera FPGAʱ�ļ���SKU������ʱ������FPGAӦ���Ѿ��������-��������Stratix��Ʒ�߶���MCP��Ʒ��������չʾ��(δ��װ��)��������Ĵ����ⲿGPU��Kaby Lake CPUģ���ʾ��������оƬ֮���Ƕ��ʽ�Ž�����

"������Դ�ڲ�ͬ��������оƬ�Ƿ������Եķ�װ��ɿ������⣿"�����ʵ�"������������빩Ӧ�̺��������ijɹ�"��ָ�Ÿ���MCPģ���еIJ�ͬоƬ����˵��"���������̨���磬���������GF����Щ������SKHynix��HBM�ڴ��ջ��������ȫ���Ĺ�Ӧ�̶����к������ƶ���bumpұ����Ͳ��������BEOL���������ԣ�оƬ��Ⱥ������ȣ�������ЩоƬ�Ķ���֤���Ǻϸ�ġ�"

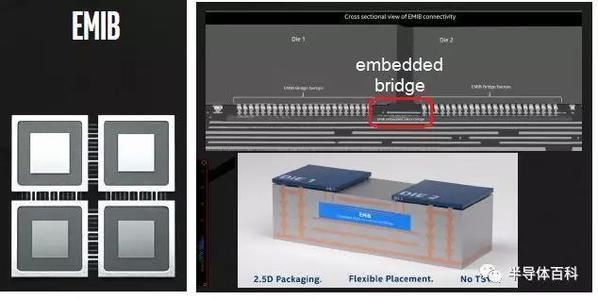

EMIB

Ƕ��ʽ���о������(EMIB)����һС�����MCP�е�������о�����ڱ�Ե֮���ṩ���ɵĻ����ԡ�EMIBĿǰ�������ĸ�������ƽ��--2���źź�2����Դ/��(��Ҫ�������Σ���Ҳ������оƬ֮���P/G����)��

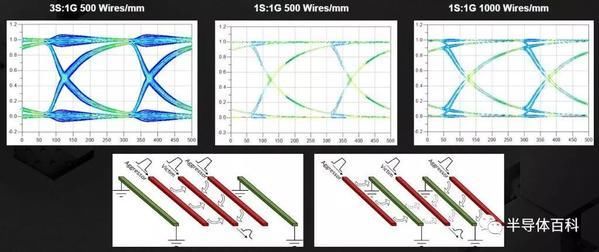

���⣬Ӣ�ض���Si�Ŷӷ����˲�ͬ���ȵ��źźͽӵ����ߵIJ�ͬ�������˵��ź����-��μ���ͼ��

Ӣ�ض��о�ԱRavi Mahajan�ṩ���й�EMIB������������Ϣ����ָ��EMIBƽ��Ľ�����Ƚ��ڹ�ƬRDL��ͷ�װ����֮�䣬ʵ���˻��������������֮���ƽ�⡣������������2um���߿���2um��࣬������1um�߿���1um���Ŭ�������Ƕ�EMIB��Si��������������8mm�ij��������ṩ�㹻����ͼ�������Ӹ����Ͻ���EMIB���Դﵽ~200ƽ�����ס���(���磬����оƬ��Ե֮��ľ���Ϊ25mm������Ϊ8mm)

Ŀǰ���Ž�������ƺ�������Ӣ�ض�ATTD���-����û���ⲿ�����������ATTD��Ƕ��ʽ�Ž���������оƬ��I/O����ƽ��ͼ�Ŀ�����һ��Э��Ŭ��������Ram��ʾ������VDD IO��GND IO�������Ҳ�����˴�������װ��EMIB��Χ��оƬ�ϵ��ܱ�bump���еĵ�ѹ���䡣Ӣ�ض�ATTD���Ը��Ϸ�װ��ƽ������Ⱥͻ�е�����Է���������MPC�����г���ɢ��ˮƽ���ܸܺߣ���������оƬ��EMIB����л�����֮���������ϵ����ͬ�����bump�Ӵ���������е���ܷ���������Ҫ��

�Զ�����ֵ��һ����ǣ���װ��EMIB��Ĵ��ڲ�����Ž�������װ��ԴԪ�����ӵ���������Ĵ�ͳ����(���磬ȥ��ñ)�������ֻ��ϣ��Ա����װ�������������SMTñ��֧�ֵõ���ǿ��-����22nm���սڵ�������Ӣ�ض�CPU��װ�����˵�ѹ���ں͵�ѹ����ơ���װ�ϵĵ�к͵���Ԫ������ѹ�������ʹ�õĽ�ѹת������һ���֡�����Ramָ������Ӣ�ض��������MCP�Ŀͻ�Ҳ���Ի�ô˹���֧�֡�

����EMIB����Ƶ�������ʹ�ù��н���2.5D��װ��Ʒ�кܴ�ͬ��һ���棬���ڽ��ʲ��Խ������������Si���ʲ㸳����оƬ�����Ӹ��������ԡ�(���µ�2.5D��Ʒ�ṩ����ϡ������ع�֮������Ӽ��߹��գ����ṩ����1X�����ֳ��ߴ�Ľ��ʲ���ơ�)�෴�أ�EMIB����רע������оƬ��Ե(����ƽ��)���ӡ������ֻ����ᵽ��������Ž������ɵ���ͳ��װ��������շ�װ������ʹ��100mmx100mm���ʲ�ߴ���500mm��500mm�л���������ϳ�Ϊ���ܡ������л������EMIBʵ���˿ɹ۵ijɱ��Ż�

3D��Foveros��

����Lakefield CPU��Ʒϵ�У�Ӣ�ض��Ƴ��˲��ù�ͨ��3DоƬ�ѵ���װ��Ʒ����ͼ˵����3DоƬ��ջ��

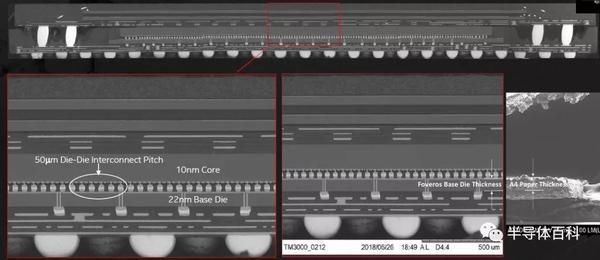

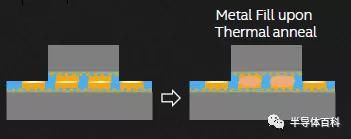

����װ�з����ص��Ǽ���TSV����Ľھ��С-Ŀǰ�Ľھ�Ϊ50um��Ŀ����Ϊ30-35um���⽫��Ҫ����ѹճ��ת��Ϊ���صġ����ճ�ϡ�����-����ͼ��

��ѹ�������ѹ�����¶����ں�����ģ���ϵ���¶����ұ�𣬶���Ͻ��ʼ��(��Щ��µ�)��գ�����ģ�߱����ṩ���м�����ȷ���Ƶġ����ݡ��ĺ��̽�������ϲ�������(��ˮ�ģ�����ƽ���)ģ�߱���֮��ķ��»�����Ȼ�����˻������ʹ���������Բ����������ӡ�

��һ���ؼ���3D��װ�з���ע�ص���ѹ��оƬ���-��3D��װ��Ŀ���Ǽ���ѹ����������ĺ�ȡ����ѵ�оƬ�ı����Ӿ���װ��Ϳɿ������⡣����Ravi M.ǿ��˵��������һ����Ȥ���Ӿ����ӣ������ǵ���һ��A4ֽ������оƬ�IJ���������Ҫ��(��ʼ300mm��Բ��ȣ�~775um;A4ֽ�ź�ȣ�~50um)

�ڲ��õĽ����������3DоƬ�����Ϊ����2.5D���˵�һ���ֵ����������ṩ������Intel ATTD��ʾΪ��co-EMIB������ͼ˵����3D�ѵ�оƬ��ѵ�֮��Ƕ��ʽ�Žӵ���ϸ��

Chiplets,KGD��s,and AIB MCP�����ļ��ٲ��ý������ڹ㷺��оƬ�鹩Ӧ���䷽ʽ������SoC�е�ӲIP���ܡ�����������Ӣ�ض�ATTD�Ŷ��Ѿ��������Ҫ��Դ�������������⣬��ȷ������װ/���Բ����Ϳɿ��ԡ�Ȼ����СоƬI/O֮��ĵ������ܽӿڶ�����Ҫ��������ҵ��Χ�ڼ��о������б�������ȷ��оƬ���Ļ������ԡ�

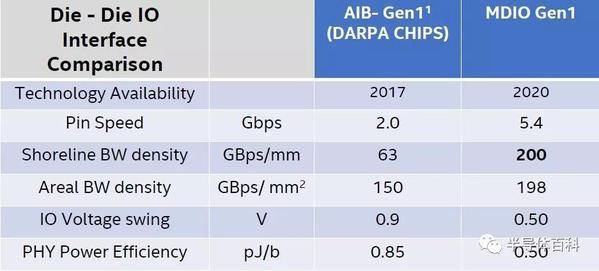

Ӣ�ض��ѷ�����AIB�淶��������DARPA��CHIPS���ƻ��Ļ��������ߣ����ƹ�оƬ������(DARPA���ӣ�AIB����-��Ҫע��)��Щ���˾��ȵ��ǣ�IEEE�ƺ�û�л�������������-�ܿ죬�������ʡ�

�����ֻ��ϣ�Ӣ�ض�ATTD�Ŷӱ�ʾ����һ��оƬ���ӿڹ淶(MDIO)���ڽ����ڲ����Ŀ���ǽ��������ʴ�2Gbps��ߵ�5.4Gbps(�ڽϵ͵ĵ�ѹ�ڷ����Ż�����)��

MCP��Ʒ��ƽ��������У������õ�������Ҫһ����ȷ�ı�-������СоƬ��������̫����������DARPA��Andreas Olofsson��������������

����оƬ����ƻ�����һ�����棬�����ֻ��Ͻ����˼�Ҫ���ۡ�MCP�����պ�������Բ��ʽ�ȡ������֪������Ƭ(KGD)СоƬ�IJ��ԺͿɿ���������ATTD�Ŷӱ�ʾ��Ӣ�ض��Ѷ�����ATE�豸���������˳���(�ڲ�)Ͷ�ʡ�ͻ����һ���ض��������ܹ��ھ�Բ��ִ�м����¶�ѭ�����ԣ�����ʶ��/��������ʧЧ�C�Ա������͵���װ��װ��KGD�������ϻ���������������ʧ��СоƬ��IP���Ĺ�Ӧ�̵�ȻҲ��Ҫ�ԵͲ��Գɱ��������ṩ�߿ɿ���оƬ�����⡣

Futures

�������ֻ��ݽ�����Ӣ�ض��о�ԱJohanna Swan����������һЩ���ڽ��еĸ���װ�з���������עĿ�Ļ����ǰѼ������ӱ�ɵ�ͨ�����ӵĹ��ա�������ͼ�����Ĵ��ͨ���̵����߳ߴ���죬����δ��ͨ�ס���ʹ�����ܶ����Ÿ��ơ���ͼ˵���˵�ǰ��װ����-ͨ�����ˣ��Լ�2-4um���߿��ȵ���ZMV�������ӡ�

Ŀǰ���ڻ�����֬�ķ�װ�����ü������-ʵ��ZMV��һ���¼��������о��С�(Johanna��ʾ�������ǰ�ϵ�еĿɹ������Ͽ��ṩ�㹻�ߵ�ͨ���ܶȣ������ϣ����պͳɱ�����Ҫ��ʹ�û�����֬���C�����Ҫ���صĻ�����֬���ա�)���ZMV����ת������������MCP����(����+�ռ�)�����ܶȽ��������-��������ĸĽ�����ʱ���ڴ���MCP��ʵ�ֵ�ϵͳ�����ܽ��Ƿdz�����ӡ����̵ġ�

Summary

���ֻ��������ؼ�Ҫ�㣺

�칹��оƬ(оƬ��/��СоƬ)��װ��Ϊϵͳ�ܹ�ʦ�ṩ��Ļ���������/����/���+���/�ɱ��Ż���

����ù��н���2.5D��װ��ȣ���Ƭ�ӿڴ���Ӣ�ض�EMIB�������ṩ��һ����صijɱ�/�ߴ�/������Ȩ�⡣

Ӣ�ض�ATTD�Ŷ�������ΪѰ�����������г����ز�Ʒ��������Ŀͻ��ṩ�Ƚ���2.5D��3D�ͺϲ�(co-EMIB)����֧�֡�

̹�ʵ�˵�������������ѧʷ�ϣ�����Ӧ���Dz�Ʒ�ܹ�ʦ��������Ȥ��ʱ�ڡ�

EP3C16U484C8N

EP3C16U484C8N

EP1C6Q240C7N

EP1C6Q240C6N

EP1C6Q240I7N

EP2S90F1020I4N

EP2S90F1020C4N

EP2AGX95EF35I4N

EP2AGX95EF35C6N

EP4CE55F29CI7N

EP4CE55F29C8N

EP4CE55F29CI6N

EP4CE55F23C9N

EP4CE55F29C8LN

EP4CE55F29CI8N

EP4CE55F29C7N

EP4CE55F23C8N

EP4CE55F23C6N

EPM2210F324I3N

EPM2210F256I4N

EPM2210F324I5N

EPM2210F256I5N

EPM2210F324C4N

EPM2210F256C4N

EPM2210F324C3N

EPM2210F256C5N

EPM2210F256A5N

EPM2210F256C3N

EP3C40F780I6N

EP3C40U484A7N

EP3C40F780C8N

EP3C40Q240C8N

EP3C40F484C8N

EP3C40F484C6N

EP3C40F484C7N

EP3C40U484C7N

EP3C40U484C8N

EP3C40F780C7N

EP3C40F324A7N

EP2C5Q208I8N

EP2C5Q208C7N

EP3C120F780C7N

EP3C120F780I7N

EP3C120F484I8N

EP3C120F484I6N

EP3C120F780C8N

EP3C120F484C6N

EP3C120F484C7N

EP3C120F484C8N

EP3C120F780I6N

EP3C120F780I8N

EP3C120F780C6N

EP3C120F484I7N

XC4VSX35-10FFG668C

XC5VLX110-1FFG676I

EPC16UI88N

EP3C55F484I7N

EPM570T144C5N

EP1C6T144C8N

5M240ZT100C5N

EP4CE10E22C8N

EP1C3T144C8N

EP1C3T100C8N

EPM1270T144C5N

EPCS4SI8

EP4CE15F23C8N

EP4CE6F17C8N

EPM7064STC100-10N

EP4CE30F23C8N

EP1C12F324C8

EPCS16SI16N

EPCS16SI8N

EPM3064ATC44-10N

EPM570T100I5N

EPM7128AETC100-10N

EP3C16F484C8N

EPM3128ATC144-10N

EPCS4SI8N

EPM7064LC84-7

EP2C20F484C8

EP4CGX50CF23I7N

EPM7128STC100-15N

EPM7128STI100-10N

EP2C5T144C8N

EP2C70F672I8N

EPM7064STC44-10N

EPM7064SLC44-10N

EP1K50TC144-3N

EPM240T100C5N

EPCS64SI16N

EPM3032ATC44-10N

EPC2LC20N

EPCS1SI8N

EPF6016TC144-3N

EPM3128ATC144-7

EPC1PC8

EPM7256EQC160-12

EPM7256AEQC208-7

EP1SGX40GF1020I6

EP1K30TC144-3N

EPM7032AETC44-10N

��˾���������հ뵼������˾

��˾���ߣ�400-8855-170

��ϵ��ʽ��18926507567 QQ:549400747

��˾��ַ��www.zhjgic.com

��˾��Ӫ�������Ϻʹ洢оƬ�����ž�Ӫ�������ֻ���棬��ӭ����ʱ��ѯ