TC7W08F/7W08F顶层模块定义了系统的输人和输出

发布时间:2020/1/26 10:51:11 访问次数:4140

tc7w08f/7w08f结构级描述,前面介绍了用hdl中的过程语句,对交通灯控制系统的功能进行寄存器传输级描述。使用开发软件中的逻辑综合工具对其进行编译,就可以获得等效的门级电路描述。也可以根据构成电路的元、器件以及它们之间的连接关系,直接对交通灯控制系统进行结构级描述。

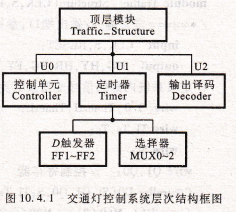

根据图10.2,6所示的交通灯控制系统结构可知,电路由三部分组成:控制单元、定时器和输出译码电路。按照数字系统自上而下分模块、分层次的设计方法,整个系统hdl描述分为三个层次,如图10.4.1所示。顶层系统的hdl描述是由控制单元、定时器和输出译码电路三部分的hdl描述组成。而控制单元又由底层的两个d触发器和3个4选1数据选择器构成。

例10.4.2给出了交通灯控制系统结构,交通灯控制系统层次结构框图,定时器timerd触发器ff1~ff2,用可编程逻辑器件,实现数字系统顶层模块,控制单元输出译码选择器.

结构级hdl描述,它由6个模块构成,可以分为4部分:

第一个顶层模块调用3个设计块。调用时端口采用了两种连接方式,u0、u2是位置对应的调用方式,即调用时端口的排列顺序必须跟下层模块定义时端口的排列顺序一致;u1是端口名称对应的调用方式,端口顺序可任意排列,圆括号内部是顶层模块使用的端口名称,圆括号外部是下层模块使用的端口名称。

后面3个模块描述了控制单元u、d触发器和数据选择器。第五个模块描述了定时器。

最后一个模块描述了输出电路。与寄存器传输级类似,顶层模块定义了系统的输人和输出。由于在底层说明了输出信号的类型,这里可以省略。顶层模块由后面3个模块构成,它们的输入输出端口中,有些是系统的输入输出端口,有些则是系统内其他模块产生的内部信号。例如控制模块u0的输人t1、ts、ty,是定时器u1的输出。

控制模块是根据图10.2.9描述的。其中两个d触发器的输人y2、y1和输出q1、q0均定义为wire类型,这是因为触发器现态q1、q0作为控制单元的输出是组合型的,而y2、y1是后面调用的组合电路数据选择器的输出。控制模块调用了3个选择器模块和2个d触发器模块。然后描述d触发器和数据选择器模块。数据选择器的输出y定义为reg类型,是因为always块中,被赋值的信号必须是reg型。

最后两个模块是具有同步清零的定时器和输出译码电路。其中m60、m30、m5和hg、hy、hr、fg、fy、fr定义为wire类型,是因为后面的assign语句要求被赋值的信号必须是wire型。

例10,4.2交通灯控制系统的结构级描述,定义输入/输出端口,参见图10.2.6,定义系统内部的信号变量及其类型,用于定时器的寄存器,控制寄存器数字系统设计基础.

tc7w08f/7w08f结构级描述,前面介绍了用hdl中的过程语句,对交通灯控制系统的功能进行寄存器传输级描述。使用开发软件中的逻辑综合工具对其进行编译,就可以获得等效的门级电路描述。也可以根据构成电路的元、器件以及它们之间的连接关系,直接对交通灯控制系统进行结构级描述。

根据图10.2,6所示的交通灯控制系统结构可知,电路由三部分组成:控制单元、定时器和输出译码电路。按照数字系统自上而下分模块、分层次的设计方法,整个系统hdl描述分为三个层次,如图10.4.1所示。顶层系统的hdl描述是由控制单元、定时器和输出译码电路三部分的hdl描述组成。而控制单元又由底层的两个d触发器和3个4选1数据选择器构成。

例10.4.2给出了交通灯控制系统结构,交通灯控制系统层次结构框图,定时器timerd触发器ff1~ff2,用可编程逻辑器件,实现数字系统顶层模块,控制单元输出译码选择器.

结构级hdl描述,它由6个模块构成,可以分为4部分:

第一个顶层模块调用3个设计块。调用时端口采用了两种连接方式,u0、u2是位置对应的调用方式,即调用时端口的排列顺序必须跟下层模块定义时端口的排列顺序一致;u1是端口名称对应的调用方式,端口顺序可任意排列,圆括号内部是顶层模块使用的端口名称,圆括号外部是下层模块使用的端口名称。

后面3个模块描述了控制单元u、d触发器和数据选择器。第五个模块描述了定时器。

最后一个模块描述了输出电路。与寄存器传输级类似,顶层模块定义了系统的输人和输出。由于在底层说明了输出信号的类型,这里可以省略。顶层模块由后面3个模块构成,它们的输入输出端口中,有些是系统的输入输出端口,有些则是系统内其他模块产生的内部信号。例如控制模块u0的输人t1、ts、ty,是定时器u1的输出。

控制模块是根据图10.2.9描述的。其中两个d触发器的输人y2、y1和输出q1、q0均定义为wire类型,这是因为触发器现态q1、q0作为控制单元的输出是组合型的,而y2、y1是后面调用的组合电路数据选择器的输出。控制模块调用了3个选择器模块和2个d触发器模块。然后描述d触发器和数据选择器模块。数据选择器的输出y定义为reg类型,是因为always块中,被赋值的信号必须是reg型。

最后两个模块是具有同步清零的定时器和输出译码电路。其中m60、m30、m5和hg、hy、hr、fg、fy、fr定义为wire类型,是因为后面的assign语句要求被赋值的信号必须是wire型。

例10,4.2交通灯控制系统的结构级描述,定义输入/输出端口,参见图10.2.6,定义系统内部的信号变量及其类型,用于定时器的寄存器,控制寄存器数字系统设计基础.

热门点击

热门点击

- DTSM-63K-V 判断LED数码管的好坏

- 65474-001上升沿触发和下降沿触发的D触发器逻辑符号

- HZT33-02TE 电解电容器正接时漏电电流小

- PD3327C 锯齿波电压振荡频率的变化

- IXFP34N65X2 功能识别号的机械电气属性

- XCV812E-6BGG560C 导缘和定尺的安装面

- LMU16PC-65目视检测对内部进行目视检测

- VWM350-0075P 编程软件的主要特点

- KIC3812FT 前置放大器放大倍数的调整

- T492C226K025AS 螺栓连接中的受拉和受剪2种情况

推荐电子资讯

推荐电子资讯

- iPhone5S/iPhone5C获工信部认证

- 库克一直看好中国市场的巨大潜力,并且自去年3月以来他已... [详细]

公网安备44030402000607

公网安备44030402000607