公司:深圳市创宝来科技有限公司

联系人:苏先生

联系方式:18923859947QQ:3005367043

公司网址:www.szcblic.com

专做进口原装,诚信经营,大量现货库存,欢迎您随时咨询

本振和相位噪声

本振(Local Oscillator,LO)是现代通信系统一个必不可少的组成部分。一个描述本振性能的参数是相位噪声。简单地说,相位噪声就是本振产生信号在频域上的稳定程度的衡量。相位噪声的定义是在一个给定频率偏移Δf处的dBc/Hz值,描述的是本振产生信号和期望频率之间偏差Δf的可能性。

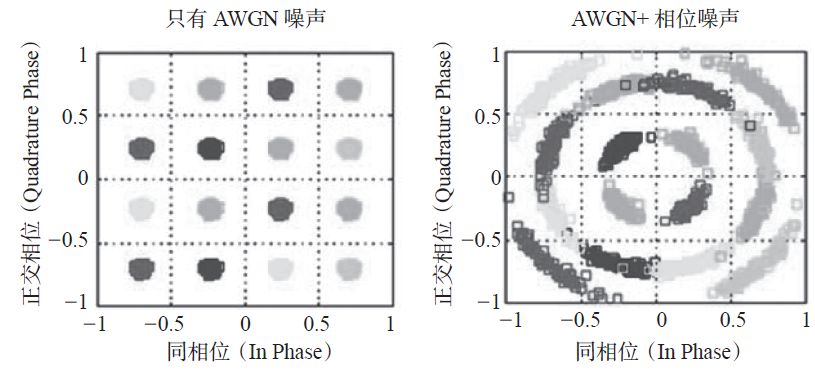

本振的相位噪声会显著影响系统性能。如图19-2所示,以单载波为例,在加入了加性高斯白噪声(Additive WhiteGaussian Noise,AWGN)建模的热噪声之后,比较了有相位噪声和没有相位噪声两种情况下的16QAM星座图。对一个给定的符号错误率门限,相位噪声会限制最高的调制阶数,如图19-2所示。换句话说,不同的调制阶数会对本振的相位噪声提出不同的要求。

自由振荡器和锁相环的相位噪声特性

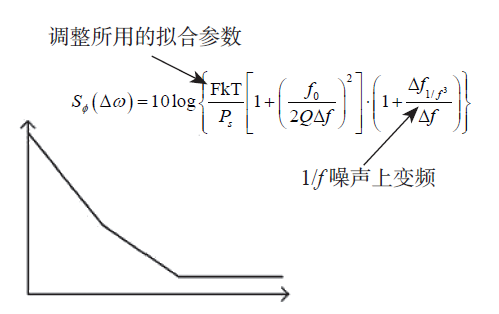

生成频率最常用的电路是压控振荡器(Voltage-ControlledOscillator,VCO)。图19-3通过一个模型来建模自由振荡的VCO对不同频率偏移的特性。

这里f0是振荡器频率,Δf是频率偏移,PS是信号强度,Q是谐振器的加载品质因子,F是经验拟合参数(对应的物理意义是噪声系数),而Δf1/f3有源设备1/f噪声的拐点频率。

根据图19-3所示公式,可以得出:

振荡器频率f0加倍,则相位噪声增加6dB。

相位噪声和信号强度Ps成反比。

相位噪声和谐振器加载品质因子Q的平方成反比。

1/f噪声上变频提升了临近载波频点位置的相位噪声(即:小频率偏移)。

因此在设计VCO的时候,需要平衡几个相关参数。为了比较不同半导体技术和电路拓扑下VCO的性能,往往使用品质因数(考虑了功耗的影响)来进行公平的比较:

其中是PNvco(f)VCO的相位噪声,单位为dBc/Hz;是功耗,单位为W。这个公式值得注意的一点是相位噪声和功耗(线性值)都与f20成正比。因此为了保持一定的相位噪声,增加频率N倍则意味着功耗需要增加N2倍(假定品质因数一定)。

一个通常的抑制相位噪声的做法是使用锁相环(Phase Locked Loop,PLL)。基本结构包括VCO、分频器(frequency divider)、相位检测器(phase detector)、环路滤波器(loop filter)和一个高稳定性低频参考源(比如晶振)。锁相环输出的相位噪声来源包括:

在环路滤波器带宽之外的VCO相位噪声部分。

环路之内的参考振荡器产生的相位噪声。

相位检测器和分频器的相位噪声。

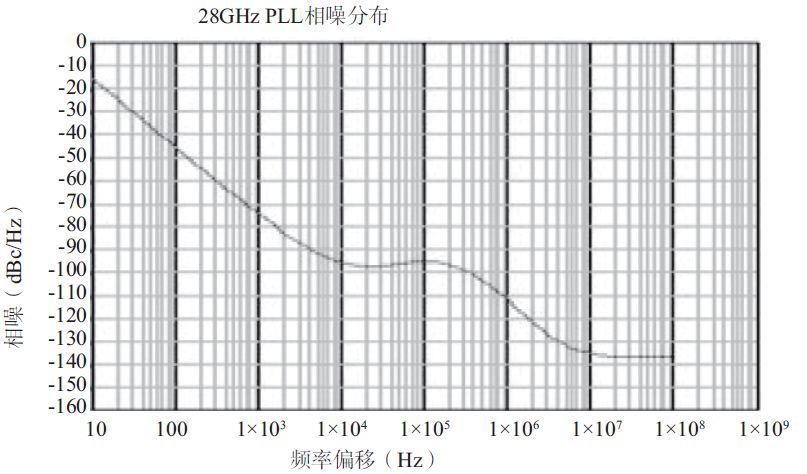

图19-4提供了一个典型的毫米波本振的特性,显示了一个28GHz本振相位噪声的测量结果。该本振在低频使用了锁相环然后倍频到28GHz。可以观察到有4个不同特点的区间:

f1小频率偏移<10kHz。大致按照30dB/decade的速率下降,主要来自1/f噪声上变频。

f2频率偏移在锁相环带宽之内。相对平坦并包含多种噪声来源。

f3频率偏移大于锁相环带宽。大致按照20dB/decade的速率下降,主要来自VCO相位噪声。

f4更大的频率偏移>10MHz。平坦,主要来自底噪。

毫米波信号生成的挑战

当振荡器频率从3GHz提升到30GHz,相位噪声也会随之提升。对特定频率偏移,相位噪声会恶化20dB数量级。这显然会限制毫米波可用调制模式的最高阶,最终限制毫米波的最高频谱效率。

毫米波本振同样受限于品质因子Q和信号强度Ps。Lesson方程指出,为了获得较低的相位噪声,必须提高品质因子Q和信号强度Ps,同时降低有源器件的噪声系数。不幸的是,当本振频率提高的时候,上述三个方面往往朝着不好的方向变化:

对单片压控振荡器(monolithic VCO),振荡器的品质因子Q会随着频率增加而快速降低。主要的原因是:(1)寄生损耗(parasitic loss)增加,诸如金属损耗(metal loss)或衬底损耗(substrate loss)增加。(2)变容二极管Q降低。

信号强度受限。这主要因为高频操作需要更加先进的半导体设备,其击穿电压也会随着尺寸的降低而降低。这些因素的影响在19.3节里介绍的功放部分也能观察到,功放也会随着频率的增加而导致功放能力的下降(-20dB/decade)。

基于这些原因,在实现毫米波本振的时候,一般都是利用一个相对低频的锁相环然后倍频到目标频点上。

除了上述的挑战,1/f噪声上变频也提升了临近载波相位噪声。当然1/f噪声和实现技术非常相关,相比于垂直双极器件(vertical bipolar device)如双极和HBT,一些平面器件诸如CMOS和高电子迁移率晶体管(High Electron Mobility Transistor,HEMT)会产生更高的1/f噪声。

为了完全集成MMIC/RFIC VCO和锁相环,可以采用各种技术(从CMOS和BiCMOS到III-V族材料)。但是因为较低的1/f噪声和较高的击穿电压,一般InGaP HBT是最为常用的。尽管有较为严重的1/f噪声,少数情况下也会采用pHEMT设备。一些方案使用GaN FET结构,尽管可以获得很高的击穿电压,但是1/f噪声甚至会比GaAS FET器件设备还要高。图19-5总结了不同的半导体技术,在100kHz频偏范围内相位噪声性能和振荡器频率的关系。

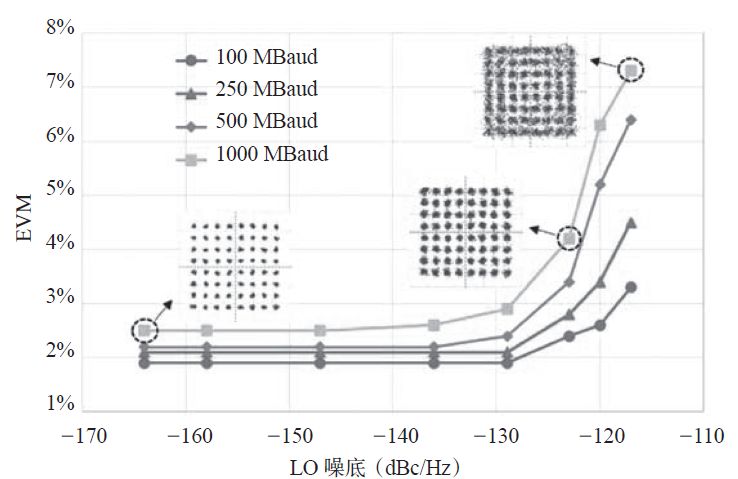

最近的研究成果揭示了本振噪底对系统性能的影响。在符号速率比较低的情况下噪底对系统影响不大。但是当符号速率提高之后,比如5G NR,平坦噪底开始对调制后的信号EVM产生影响。如图19-6所示为不同的符号速率和不同的噪底水平下测量发射信号的EVM结果。这类观察意味着为宽带通信进行毫米波本振系统设计的时候,需要额外关注技术的选择、VCO拓扑和倍频系数,以期得到合理的较低相位噪声的噪底。

5G 在物联网领域的技术应用实践

以上仅为毫米波技术的部分,而为了帮助通信从业者、物联网开发者、嵌入式程序员们更好了解并应用 5G 技术,CSDN 作为主办方特别策划以“5G 在物联网领域的技术应用实践”为主题的沙龙活动,邀请到来自爱立信中国研发部多天线高级专家朱怀松、爱立信中国研发部主人系统工程师刘阳,基于全新的 5G 标准,分享其在实践中帮助解决物联网各式各样需求的方案。

从而让开发者们得以深入了解无线物联网需求的多样性,以及 5G 是如何通过一个统一的框架来满足未来的物联网领域的需求的。此外,两位专家还将探讨相较几乎满足了人和互联网连接需求的 4G,5G 在应用过程中还能够提供哪些特有的功能满足物联网的应用。